Configur – Altera CPRI IP Core User Manual

Page 141

Chapter 7: Software Interface

7–25

Ethernet Registers

December 2013

Altera Corporation

CPRI MegaCore Function

User Guide

mac_check

[5]

RW

Enable check of Rx Ethernet MAC address.

1’h0

length_check

[4]

RW

Indicates that a length check is performed on Rx packets,

and those with length less than 64 bytes are discarded.

1’h0

mac_reset

[3]

RW

Reset the Ethernet MAC.

1’h1

RSRV

[2]

RO

Reserved.

1’h0

little_endian

[1]

RW

Indicates that the Ethernet channel receive and transmit

data is formatted in little endian byte order.

1’h0

RSRV

[0]

RO

Reserved.

1'h0

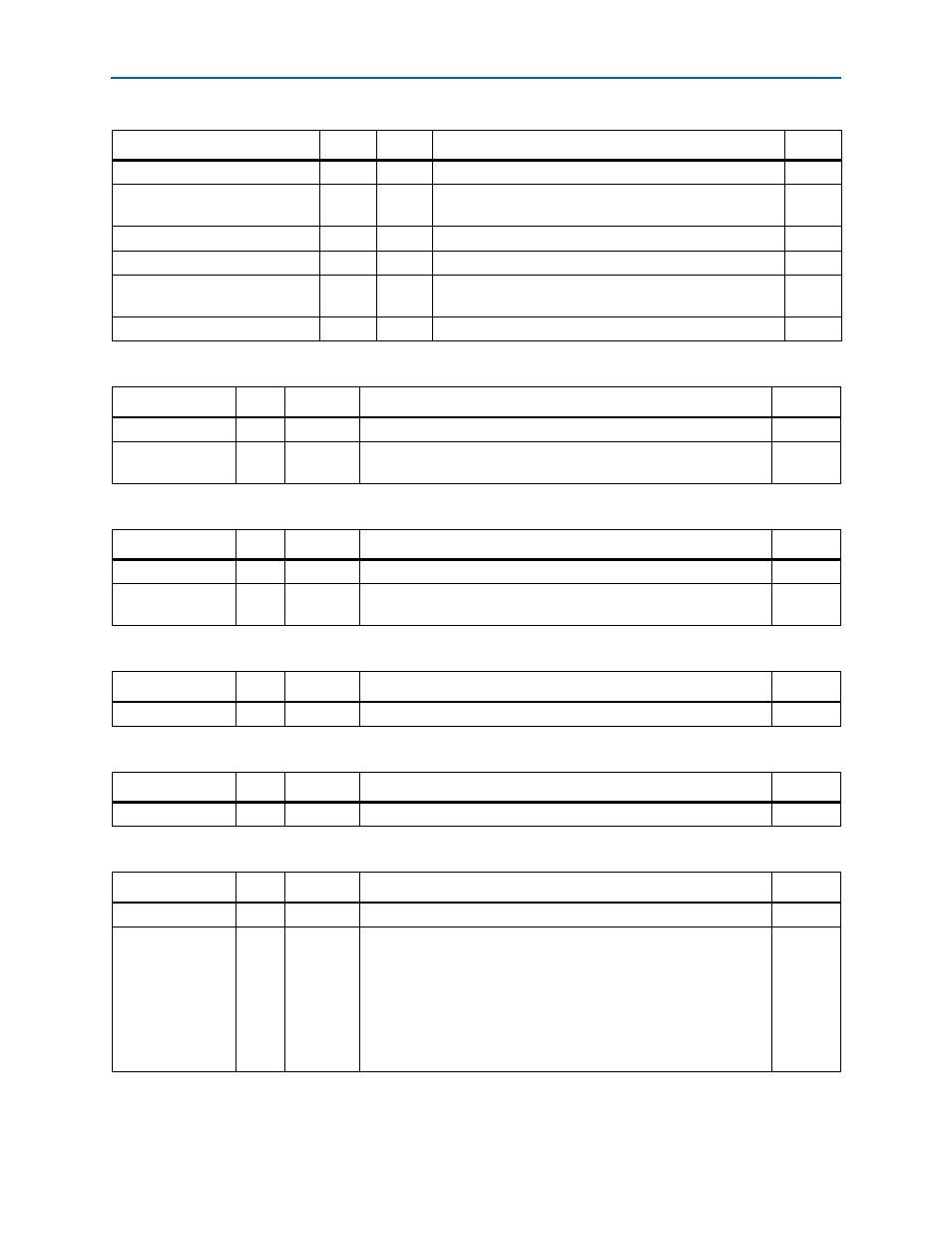

Table 7–53. ETH_CONFIG_1—Ethernet Feature Configuration 1—Offset: 0x208 (Part 2 of 2)

Field

Bits

Access

Function

Default

Table 7–54. ETH_CONFIG_2—Ethernet Feature Configuration 2—Offset: 0x20C

Field

Bits

Access

Function

Default

RSRV

[31:1] UR0

Reserved.

31'h0

crc_enable

[0]

RW

Enables insertion of Ethernet frame check sequence (FCS) at the end

of the Ethernet frame.

1'h0

Table 7–55. ETH_RX_CONTROL—Ethernet Rx Control—Offset: 0x210

Field

Bits

Access

Function

Default

RSRV

[31:1] RO

Reserved.

31'h0

rx_discard

[0]

WO

Indicates that the Ethernet receiver module should discard the

current Ethernet Rx frame.

1'h0

Table 7–56. ETH_RX_DATA—Ethernet Rx Data—Offset: 0x214

Field

Bits

Access

Function

Default

rx_data

[31:0] RO

Ethernet Rx frame data.

1'h0

Table 7–57. ETH_RX_DATA_WAIT—Ethernet Rx Data with Wait-State Insertion—Offset: 0x218

Field

Bits

Access

Function

Default

rx_data

[31:0] RO

Ethernet Rx frame data.

1'h0

Table 7–58. ETH_TX_CONTROL—Ethernet Tx Control—Offset: 0x21C (Part 1 of 2)

Field

Bits

Access

Function

Default

RSRV

[31:4] UR0

Reserved.

28'h0

tx_length

[3:2]

WO

Length of the final word in the packet. Values are:

00: 1 valid byte

01: 2 valid bytes

10: 3 valid bytes

11: 4 valid bytes

This field is valid when the

tx_eop

bit is asserted.

2’h0