Altera CPRI IP Core User Manual

Page 36

4–4

Chapter 4: Functional Description

Clocking Structure

CPRI MegaCore Function

December 2013

Altera Corporation

User Guide

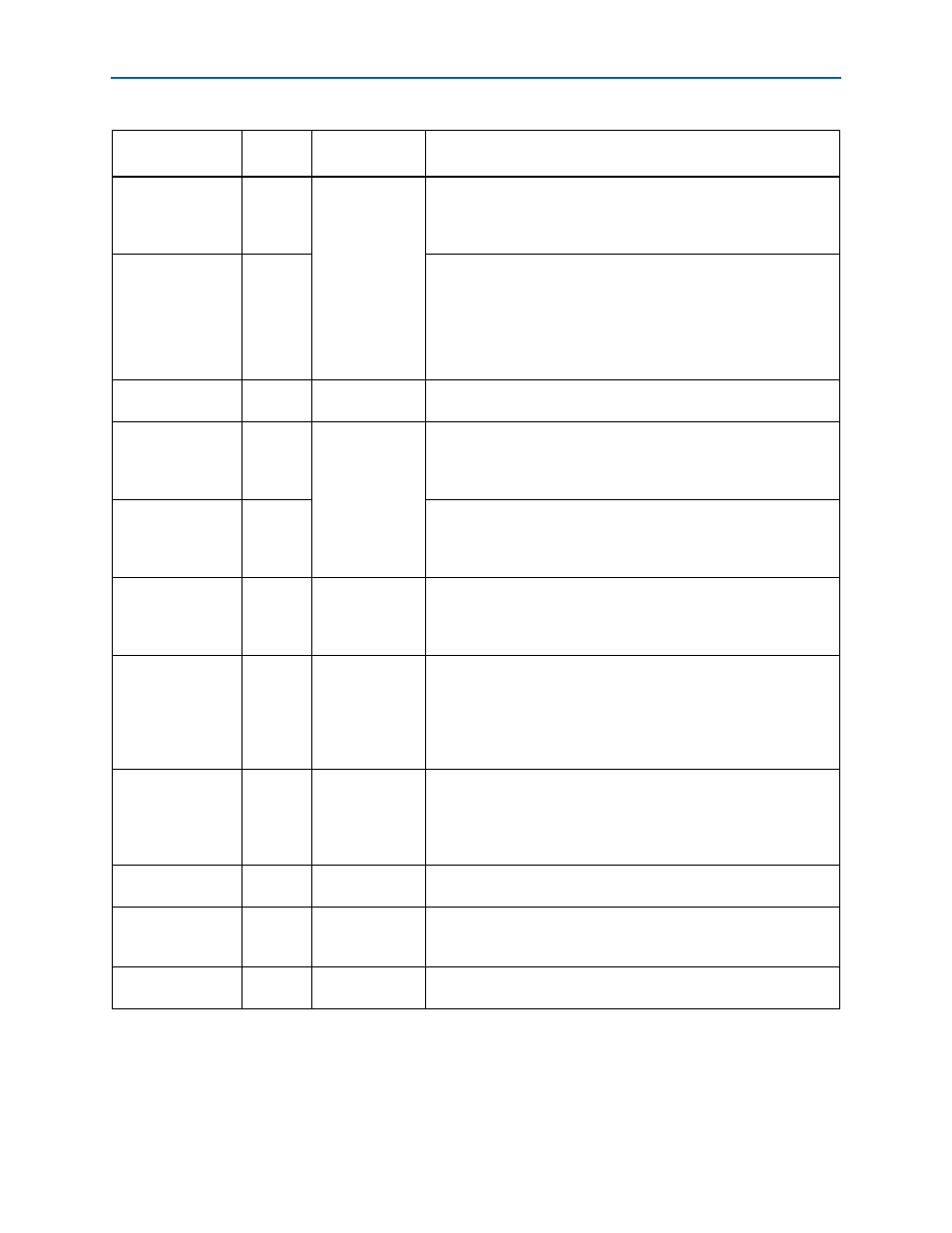

mapN_tx_clk

for

N

in

0..(N_MAP–1)

Input

Present in

variations

configured with

N_MAP > 0

antenna-carrier

interfaces and

with Enable MAP

interface

synchronization

with core clock

turned off

Expected rate of received data on antenna-carrier interface N. The

frequency of this clock is the sample rate on the incoming

antenna-carrier interface. For more information about data channel

sample rates, refer to

Table 4–5

and

mapN_rx_clk

for

N

in

0..(N_MAP–1)

Input

Clocks the transmissions of antenna-carrier interface N. The

frequency of this clock is the sample rate on the outgoing

antenna-carrier interface. For more information about data channel

sample rates, refer to

Table 4–5

and

clk_ex_delay

Input

Present in all

CPRI IP cores

Clock for extended delay measurement. For more information refer to

“Extended Rx Delay Measurement” on page E–6

.

cpri_mii_txclk

Output

Present in

variations

configured with

an MI interface

Clocks the MII transmitter module. This clock has the same

frequency as the

cpri_clkout

clock. The frequency depends on the

CPRI line data rate. Refer to

“CPRI Communication Link Line Rates”

.

cpri_mii_rxclk

Output

Clocks the MII receiver module. This clock has the same frequency as

the

cpri_clkout

clock. The frequency depends on the CPRI line

data rate. Refer to

“CPRI Communication Link Line Rates” on

cpu_clk

Input

Present in all

CPRI IP cores

Controls the input to the CPU interface of the CPRI IP core and drives

the CPU interface. Assumed to be asynchronous with the

cpri_clkout

clock. The maximum frequency is constrained by f

MAX

and can vary based on the device family and speed grade.

gxb_refclk

Input

Present in all

CPRI IP cores

Reference clock for the transceiver PLLs. In master clocking mode,

this clock drives both the receiver PLL and the transmitter PLL in the

transceiver. In slave clocking mode, this clock drives the receiver

PLL.

In master clocking mode, you must tie this input to the same source

as

gxb_pll_inclk

.

gxb_cal_blk_clk

Input

Not present in

variations that

target an Arria V,

Cyclone V, or

Stratix V device

Transceiver calibration-block clock.

reconfig_clk

Input

Present in all

CPRI IP cores

Transceiver dynamic reconfiguration block clock.

gxb_pll_inclk

Input

Present in all

CPRI IP cores

Input clock to the transmitter PLL in a CPRI IP core configured in

slave clocking mode. In master clocking mode, you must tie this

input to the same source as

gxb_refclk

.

pll_clkout

Output

Present in all

CPRI IP cores

Generated from transceiver clock data recovery circuit. Intended to

connect to an external PLL for jitter clean-up in slave clocking mode.

Table 4–1. CPRI IP Core Clocks (Part 2 of 3)

Clock Name

Direction

Configuration

Requirements

Description