Cpri communication link line rates, Cpri communication link line rates –10, Cpri – Altera CPRI IP Core User Manual

Page 42: Cpri communication link line rates” on

4–10

Chapter 4: Functional Description

Clocking Structure

CPRI MegaCore Function

December 2013

Altera Corporation

User Guide

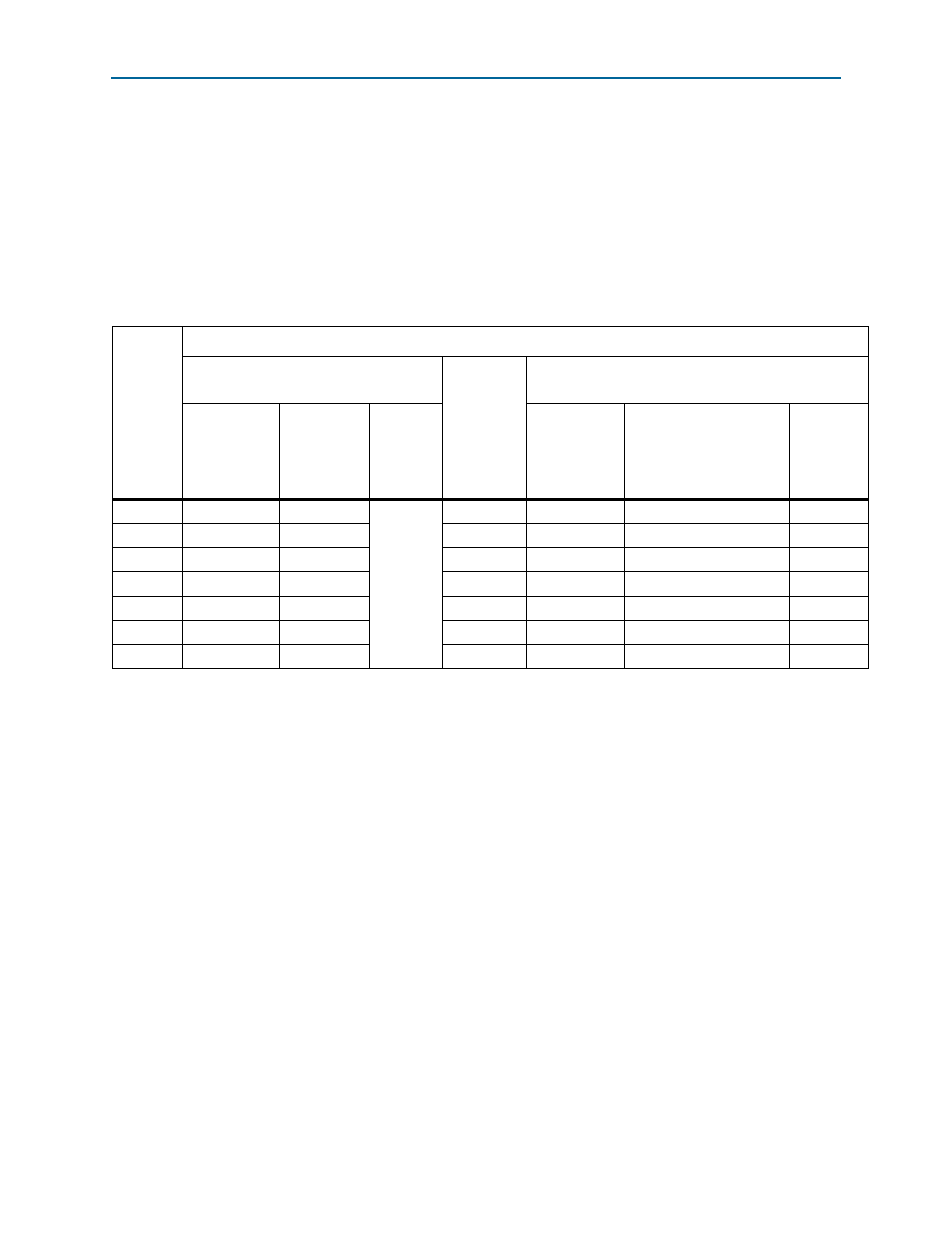

CPRI Communication Link Line Rates

The CPRI specification specifies line rates of n × 614.4 Mbps for various values of n.

The CPRI IP core supports different ranges of line rates in different device families.

lists the CPRI line rate support available in the different device

families.

Table 4–2

shows the relationship between line rates, default transceiver reference

clock (

gxb_refclk

) rates, parallel recovered clock (

pll_clkout

) rates, and internal

clock (

cpri_clkout

) rates.

The

cpri_clkout

frequency depends only on the CPRI line rate. The

pll_clkout

frequency depends on the CPRI line rate and on the datapath width through the

transceiver, except in Arria V, Cyclone V, and Stratix V devices. The

pll_clkout

frequency in an Arria V GT device depends on whether the IP core was originally

configured with the CPRI line rate of 9.8304 Gbps, and whether or not the IP core

CPRI line rate is modified dynamically through auto-rate negotiation. The datapath

width is determined by device family, as shown in

Table 4–17 on page 4–59

.

The

gxb_refclk

clock is the incoming reference clock for the device transceiver’s PLL.

Altera allows you to program the transceiver to work with any of a set of

gxb_refclk

frequencies that the PLL in the transceiver can convert to the required internal clock

speed for the CPRI IP core line rate. The parameter editor in which you configure the

gxb_refclk

frequency depends on the target device family for your CPRI IP core

variation.

Table 4–2. CPRI Link Line Rates and Clock Rates for CPRI MegaCore Function

Line Rate

(Mbps)

Clock Frequency (MHz)

Default gxb_refclk Frequency

(If line rate is supported)

cpri_clkout

Frequency

(If line rate

is

supported)

pll_clkout Frequency

(If line rate is supported)

Arria II GX

and

Cyclone IV GX

Devices

Arria II GZ

and

Stratix IV GX

Devices

Arria V

Cyclone V

and

Stratix V

Devices

Arria II GX

and

Cyclone IV GX

Devices

Arria II GZ

and

Stratix IV GX

Devices

Arria V

Cyclone V

and

Stratix V

Devices

Arria V GT

Devices

Configured

at 9830.4

Mbps

614.4

61.44

61.44

15.36

61.44

61.44

61.44

—

1228.8

61.44

61.44

30.72

61.44

30.72

30.72

61.44

2457.6

122.88

61.44

61.44

122.88

61.44

61.44

122.88

3072

153.60

76.80

76.80

153.60

76.80

76.80

153.6

4915.2

(4)

245.76

122.88

122.88

245.76

122.88

122.88

61.44

6144

(4)

307.20

153.60

153.60

307.20

153.60

153.60

76.8

—

—

245.76

—

—

245.76

122.88

Notes to

Table 4–2

:

(1) In this table, device families can be grouped with other device families that do not support all of the same CPRI line rates. The values apply only for

supported CPRI line rates for each device family.

(2) This column lists the

pll_clkout

frequencies for Arria V GX and Arria V GZ devices, as well as Arria V GT devices that are originally configured at

a CPRI line rate less than 9803.4 Mbps.

(3) The value of

gxb_refclk

in CPRI IP cores that target a 28-nm device (Arria V, Cyclone V, or Stratix V device) is the Transceiver reference clock

frequency parameter value that you set in the CPRI parameter editor.

(4) The CPRI IP core does not support CPRI line rates 4915.2 Mbps and 6144 Mbps in variations that target Cyclone IV GX or Cyclone V GX devices.

(5) The CPRI IP core supports CPRI line rate 9830.4 Mbps in variations that target Stratix V (GX or GT), Arria V GT, or Arria V GZ devices. The CPRI IP

core does not support CPRI line rate 9830.4 Mbps for any other devices, including Arria V GX devices.