Test sequence – Altera CPRI IP Core User Manual

Page 166

C–4

Appendix C: CPRI Autorate Negotiation Testbench

Test Sequence

CPRI MegaCore Function

December 2013

Altera Corporation

User Guide

Test Sequence

The testbench starts by resetting the CPRI IP core.

Table C–2

lists the frequencies of

the clock inputs to the CPRI IP core.

After the CPRI IP core comes out of the reset state, the testbench programs the

CPRI_CONFIG

register and various other IP core registers for the appropriate

functionality. The CPRI IP core starts the frame synchronization process to detect the

presence of a partner and establish frame synchronization.

When frame synchronization completes, the value on the

cpri_rx_state

output port

(bits [1:0] of the

extended_rx_status_data

bus) is 0x3 and the value on the

cpri_rx_cnt_sync

port (bits [4:2] of the

extended_rx_status_data

bus) is 0x1.

Following the appearance of these values, the value of the

cpri_rx_hfn_state

output

signal transitions to value 1, and then value of the

cpri_rx_bfn_state

output signal

transitions to value 1. When these values appear in the waveform display, the CPRI

link is up and ready to receive and send data.

The testbenches then perform autorate negotiation. The individual testbenches

attempt autorate negotiation, and successfully negotiate, at the following CPRI line

rates:

■

Stratix IV GX and Cyclone IV GX variations:

a. Achieve BFN synchronization at 0.6144 Gbps, then lose it.

b. Attempt autorate negotiation to 1.2288 Gbps; succeed at 1.2288 Gbps.

c. Lose synchronization.

d. Attempt autorate negotiation to 0.6144 Gbps; succeed at 0.6144 Gbps.

■

Most Arria V, and all Cyclone V and Stratix V variations:

a. Achieve BFN synchronization at 1.2288 Gbps, then lose it.

b. Attempt autorate negotiation to 0.6144 Gbps; succeed at 0.6144 Gbps.

■

Arria V GT variations configured at CPRI line rate 9.8 Gbps:

a. Achieve BFN synchronization at 9.8304 Gbps, then lose it.

b. Attempt autorate negotiation to 6.144 Gbps; succeed at 6.144 Gbps.

Refer to

Appendix B, Implementing CPRI Link Autorate Negotiation

for details.

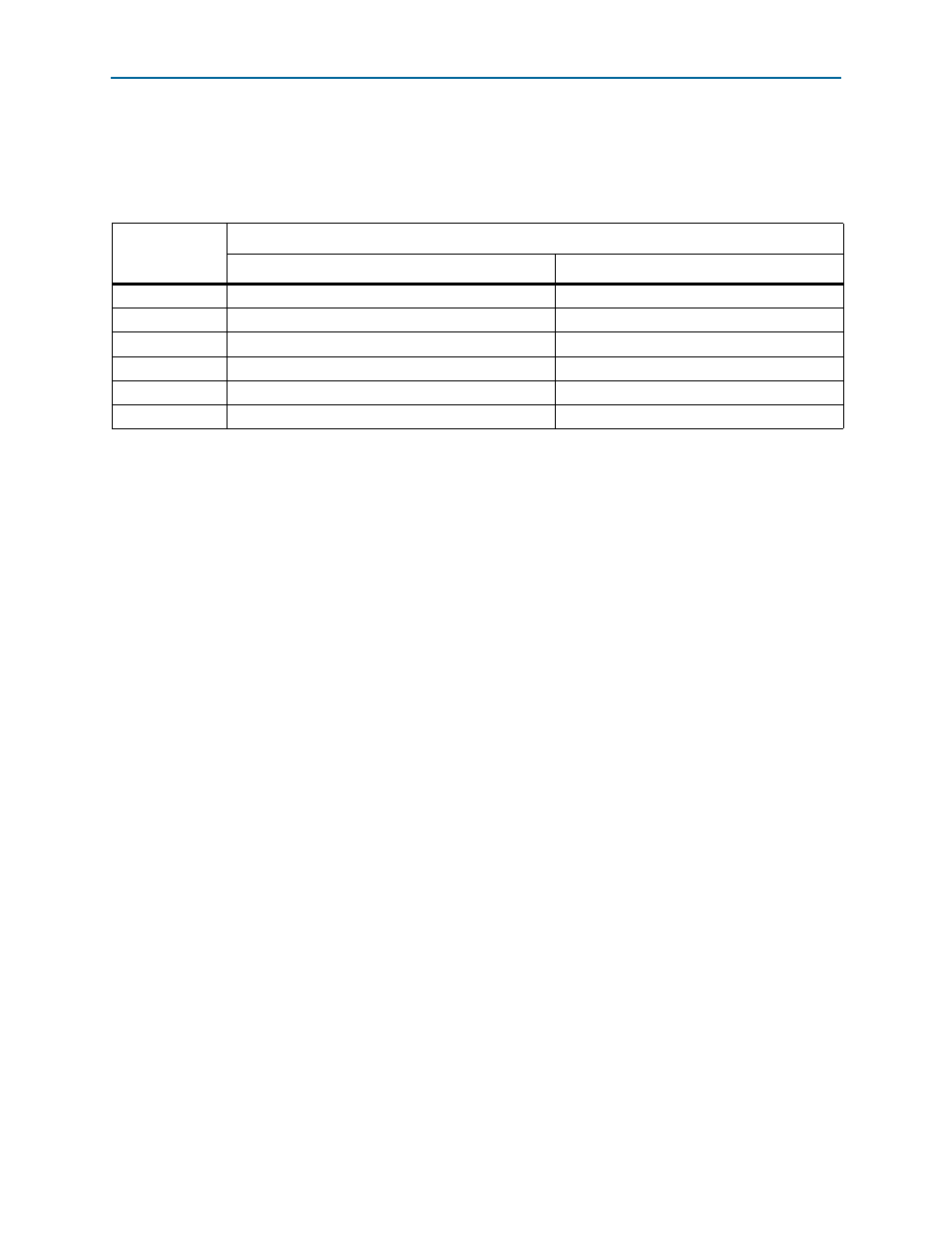

Table C–2. Clock Frequencies for CPRI IP Core Under Test

Clock

Frequency (MHz)

Arria V GT 9.8 Gbps autorate negotiation testbench

All other autorate negotiation testbenches

gxb_refclk

122.88

61.44

usr_clk

245.76

—

usr_pma_clk

122.88

—

cpu_clk

30.72

30.72

clk_ex_delay

30.96

30.96

mapN_tx_clk

3.84

3.84