Transceiver signals, Transceiver signals –15 – Altera CPRI IP Core User Manual

Page 113

Chapter 6: Signals

6–15

Physical Layer Signals

December 2013

Altera Corporation

CPRI MegaCore Function

User Guide

Transceiver Signals

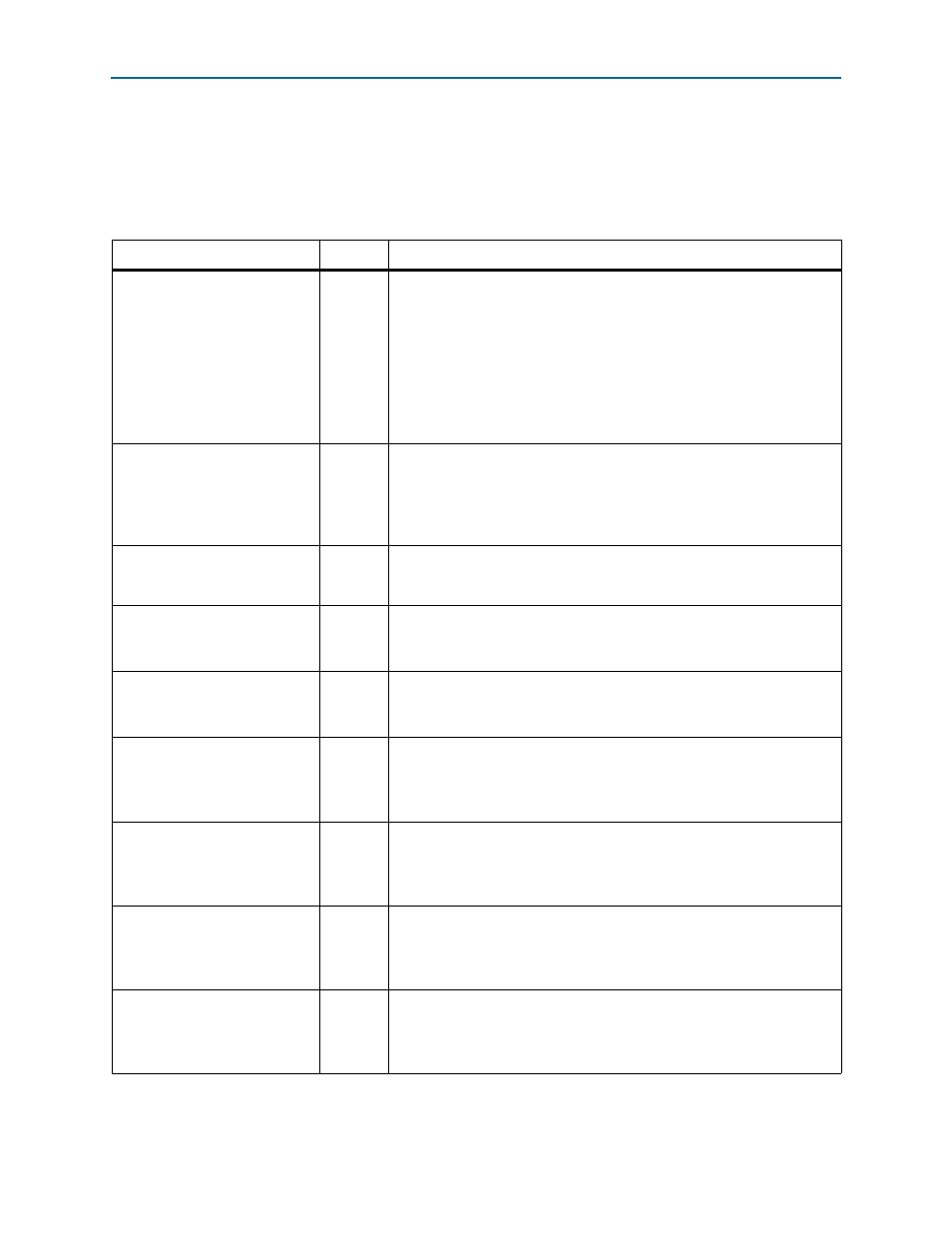

Table 6–14

lists the transceiver signals that are connected directly to the transceiver

block. In many cases these signals must be shared by multiple transceiver blocks that

are implemented in the same device.

Table 6–14. Transceiver Signals (Part 1 of 3)

Signal Direction

Description

gxb_cal_blk_clk

Input

The Arria II GX, Arria II GZ, Cyclone IV GX, and Stratix IV GX transceivers’

on-chip termination resistors are calibrated by a single calibration block.

This circuitry requires a calibration clock. The frequency range of the

gxb_cal_blk_clk

is 10–125 MHz. For more information, refer to the

chapter in volume 2 of the

Arria II Device Handbook, the

chapter

in volume 2 of the Cyclone IV Device Handbook

in volume 2 of the Stratix IV Device Handbook.

This signal is not present in Arria V, Cyclone V, and Stratix V variations.

gxb_pll_inclk

Input

Input clock to the transceiver PLL. If the CPRI IP core is configured in

master clocking mode, you must drive

gxb_pll_inclk

and

gxb_refclk

from a common source.

In slave clocking mode, the

gxb_pll_inclk

signal connects directly to the

rx_cruclk

input signal of the transceiver’s PLL.

reconfig_clk

(1)

Input

Reference clock for the dynamic reconfiguration controller. The frequency

range for this clock is 100–125 MHz for Arria V, Cyclone V, and Stratix V

variations, and 37.5–50 MHz for all other variations.

reconfig_to_xcvr[139:0]

Input

Parallel transceiver reconfiguration bus from the Altera Transceiver

Reconfiguration Controller to the transceiver in the CPRI IP core.

This signal is present only in Arria V, Cyclone V, and Stratix V variations.

reconfig_from_xcvr[91:0]

Output

Parallel transceiver reconfiguration bus to the Altera Transceiver

Reconfiguration Controller from the transceiver in the CPRI IP core.

This signal is present only in Arria V, Cyclone V, and Stratix V variations.

reconfig_togxb_s_tx

[3:0]

(1)

Input

Driven from an external dynamic reconfiguration block to the slave

transmitter transceiver block. Supports the selection of multiple transceiver

channels for dynamic reconfiguration.

This signal is not present in Arria V, Cyclone V, and Stratix V variations.

reconfig_togxb_s_rx

[3:0]

(1)

Input

Driven from an external dynamic reconfiguration block to the slave receiver

transceiver block. Supports the selection of multiple transceiver channels

for dynamic reconfiguration.

This signal is not present in Arria V, Cyclone V, and Stratix V variations.

reconfig_togxb_m[3:0]

(1)

Input

Driven from an external dynamic reconfiguration block to the master

transceiver block. Supports the selection of multiple transceiver channels

for dynamic reconfiguration.

This signal is not present in Arria V, Cyclone V, and Stratix V variations.

reconfig_fromgxb_s_tx

[16:0]

(

[4:0]

for

Cyclone IV GX devices)

Output

Driven to an external dynamic reconfiguration block from the slave

transmitter transceiver block. The bus identifies the transceiver channel

whose settings are being transmitted to the dynamic reconfiguration block.

This signal is not present in Arria V, Cyclone V, and Stratix V variations.