Table e–10, Shows the – Altera CPRI IP Core User Manual

Page 203

Appendix E: Delay Measurement and Calibration

E–25

Single-Hop Delay Measurement

December 2013

Altera Corporation

CPRI MegaCore Function

User Guide

Round-Trip and Cable Delay Calculation Example 4: Two Different Device

Families

This example describes the calculation for the case of two link partner CPRI IP cores

configured with autorate negotiation enabled in a single-hop configuration, running

at CPRI data rate 3.072 Gbps. The REC master is configured on an Arria II GX device

and the RE slave is configured on a Stratix IV GX device.

The calculation is identical to the calculation in Example 3, except that the register

values vary, and different table columns are relevant in

Table E–1

,

Table E–3

,

, and

Table E–7

.

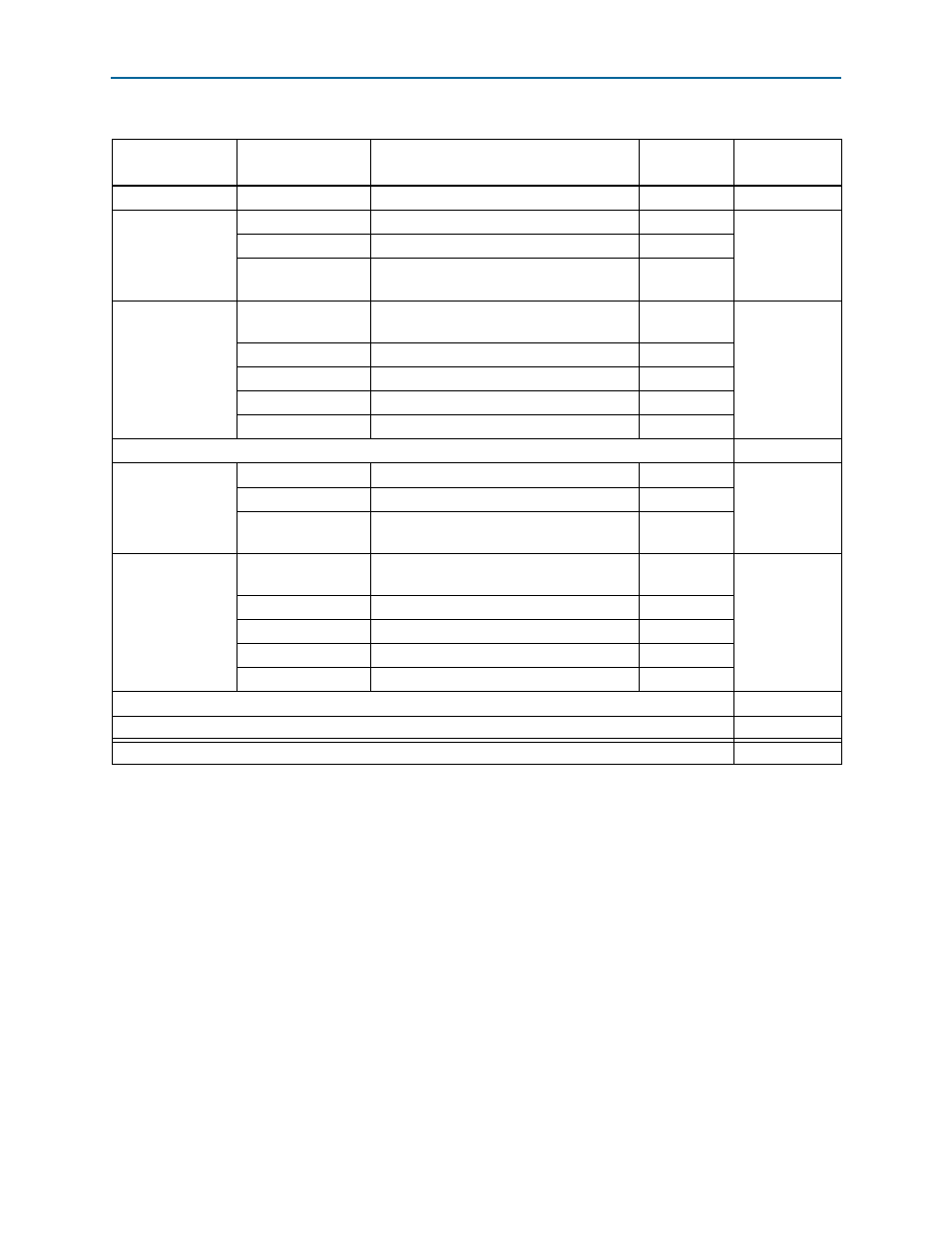

Table E–10. Example 3 Data and Calculations

Calculation

Component

Delay Component

Relevant Register Value or Source Table

Delay

Total

(decimal)

Round trip delay

rx_round_trip_delay

= 0x69

105

REC Tx path delay

T_T4

7

18.10

Tx buffer delay

tx_ex_buf_delay

= 0x3B9

7.50

T_txv_TX

tx_bitslipboundaryselect

= 0x0

Table E–7 on page E–16

3.6

REC Rx path delay

T_txv_RX

rx_bitslipboundaryselectout

= 0x8

Table E–1 on page E–5

7

47.25

Rx buffer delay

rx_ex_buf_delay

= 0x1000

32.25

Calibration pointer

cal_pointer

= 3

3

Byte alignment

rx_byte_delay

= 0

0

T_R1

Table E–3 on page E–8

5

T14 (Round trip delay minus REC Tx path delay minus REC Rx path delay)

39.65

RE Tx path delay

T_T4

6.5

18.585

Tx buffer delay

tx_ex_buf_delay

= 0x46B

8.91

T_txv_TX

tx_bitslipboundaryselect

= 0x3

Table E–7 on page E–16

3.175

RE Rx path delay

T_txv_RX

rx_bitslipboundaryselectout

= 0x5

Table E–1 on page E–5

5.575

19.475

Rx buffer delay

rx_ex_buf_delay

= 0x2ED

5.90

Calibration pointer

cal_pointer

= 3

3

Byte alignment

rx_byte_delay

= 0

0

T_R1

Table E–3 on page E–8

5

Loopback delay on RE slave

1

Toffset (RE Tx path delay + RE Rx path delay + loopback delay)

39.06

Cable delay (T14 minus Toffset)

0.59