Ethernet registers, Ethernet registers –22, Table 7–48 on – Altera CPRI IP Core User Manual

Page 138: Table 7–49 on, Table 7–49

7–22

Chapter 7: Software Interface

Ethernet Registers

CPRI MegaCore Function

December 2013

Altera Corporation

User Guide

Ethernet Registers

This section lists the Ethernet registers.

provides a memory map for the

Ethernet registers.

through

describe the Ethernet registers in the

CPRI IP core.

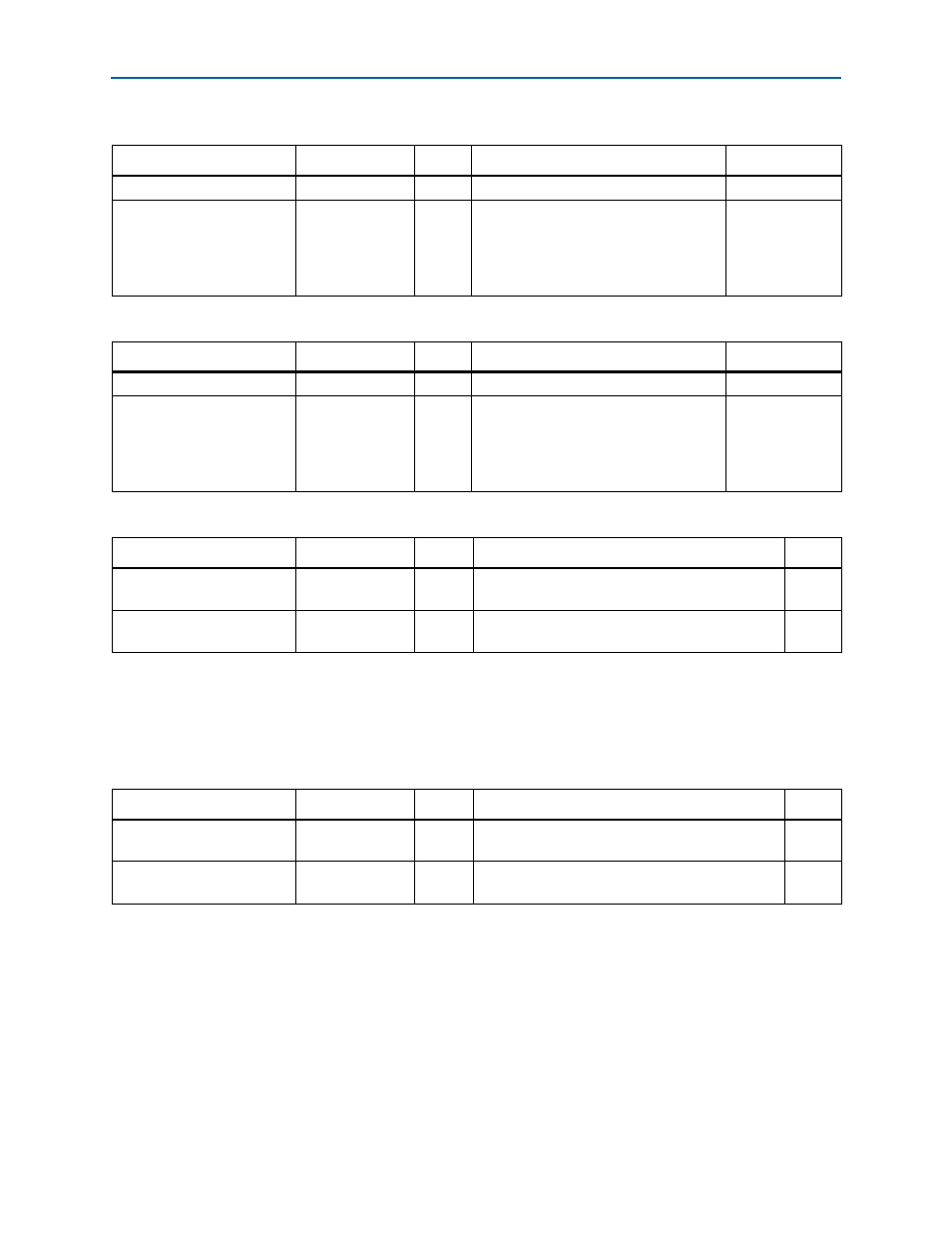

Table 7–46. CPRI_IQ_RX_BUF_CONTROL—MAP Receiver FIFO Buffer Control—Offset: 0x150

Field

Bits

Access

Function

Default

RSRV

[31:N_MAP]

UR0

Reserved.

0

map_rx_enable

[(N_MAP-1):0]]

RW

Enables or disables the corresponding

antenna-carrier receiver interfaces. The

bits of this field propagate to the

corresponding

cpri_map_rx_en

output

signals.

(N_MAP)’h7F

(all 1s)

Table 7–47. CPRI_IQ_TX_BUF_CONTROL—MAP Transmitter FIFO Buffer Control—Offset: 0x160

Field

Bits

Access

Function

Default

RSRV

[31:N_MAP]

UR0

Reserved.

0

map_tx_enable

[(N_MAP-1):0]]

RW

Enables or disables the corresponding

antenna-carrier transmitter interfaces.

The bits of this field propagate to the

corresponding

cpri_map_tx_en

output

signals.

(N_MAP)’h7F

(all 1s)

Table 7–48. CPRI_IQ_RX_BUF_STATUS—MAP Receiver FIFO Buffer Status—Offset: 0x180–0x184

Field

Bits

Access

Function

Default

buffer_rx_underflow

[(N_MAP+15):16] RC

Indicates MAP Rx buffer underflow in the

corresponding antenna-carrier interfaces.

16'h0

buffer_rx_overflow

[(N_MAP-1):0]]

RC

Indicates MAP Rx buffer overflow in the

corresponding antenna-carrier interfaces.

16'h0

Notes to

:

(1) If this CPRI IP core has more than 16 antenna-carrier interfaces (N_MAP > 16), the status for antenna-carrier interfaces 0 through 15 is in the

register at offset 0x180, and the status for antenna-carrier interfaces 16 and up is in the register at offset 0x184. The maximum number of

antenna-carrier interfaces in the CPRI IP core is 24.

(2) This register does not participate in data transfer synchronization on the antenna-carrier interfaces in the internally-clocked mode.

Table 7–49. CPRI_IQ_TX_BUF_STATUS—MAP Transmitter FIFO Buffer Status—Offset: 0x1A0–0x1A4

Field

Bits

Access

Function

Default

buffer_tx_underflow

[(N_MAP+15):16] RC

Indicates MAP Tx buffer underflow in the

corresponding antenna-carrier interfaces.

16'h0

buffer_tx_overflow

[(N_MAP-1):0]]

RC

Indicates MAP Tx buffer overflow in the

corresponding antenna-carrier interfaces.

16'h0

Notes to

:

(1) If this CPRI IP core has more than 16 antenna-carrier interfaces (N_MAP > 16), the status for antenna-carrier interfaces 0 through 15 is in the

register at offset 0x1A0, and the status for antenna-carrier interfaces 16 and up is in the register at offset 0x1A4. The maximum number of

antenna-carrier interfaces in the CPRI IP core is 24.

(2) This register does not participate in data transfer synchronization on the antenna-carrier interfaces in the internally-clocked mode.