Table 7–29, 0x64 – Altera CPRI IP Core User Manual

Page 130

7–14

Chapter 7: Software Interface

CPRI Protocol Interface Registers

CPRI MegaCore Function

December 2013

Altera Corporation

User Guide

tx_bitslipboundaryselect

[4:0]

RW

Number of bits of delay (bitslip) the CPRI IP core adds at the

CPRI Tx link to compensate for the variability in the Rx word

aligner bitslip. The purpose of this added delay is to ensure

the variability in the round-trip delay through this CPRI RE

slave remains compliant with the R-20 and R-21

deterministic latency requirements of the CPRI specification

V4.2. The device family and CPRI line rate determine the

following maximum values for this field:

■

Maximum value for all CPRI variations with line rate

614.4 Mbps and for all variations that target an Arria II GX

or Cyclone IV GX device: 9 bits.

■

Maximum value for all other variations: 19 bits.

The latency differences from different Tx bitslip delay values

are observable only with an oscilloscope.

5’h0

Notes to

:

(1) In variations that target an Arria V, Cyclone V, or Stratix V device, the Tx bitslip functionality is included in the Altera Transceiver PHY IP core

that is generated as part of the CPRI variation.

(2) CPRI variations with master clocking mode (CPRI REC and RE masters) do not support the automatic bitslip calibration functionality controlled

by this register.

(3) For information about the CPRI IP core Tx bitslip feature, refer to

“Tx Bitslip Delay” on page E–14

Table 7–28. CPRI_TX_BITSLIP— Tx Bitslip —Offset: 0x64

(1)

,

(2)

,

(3)

(Part 2 of 2)

Field Bits

Access

Function

Default

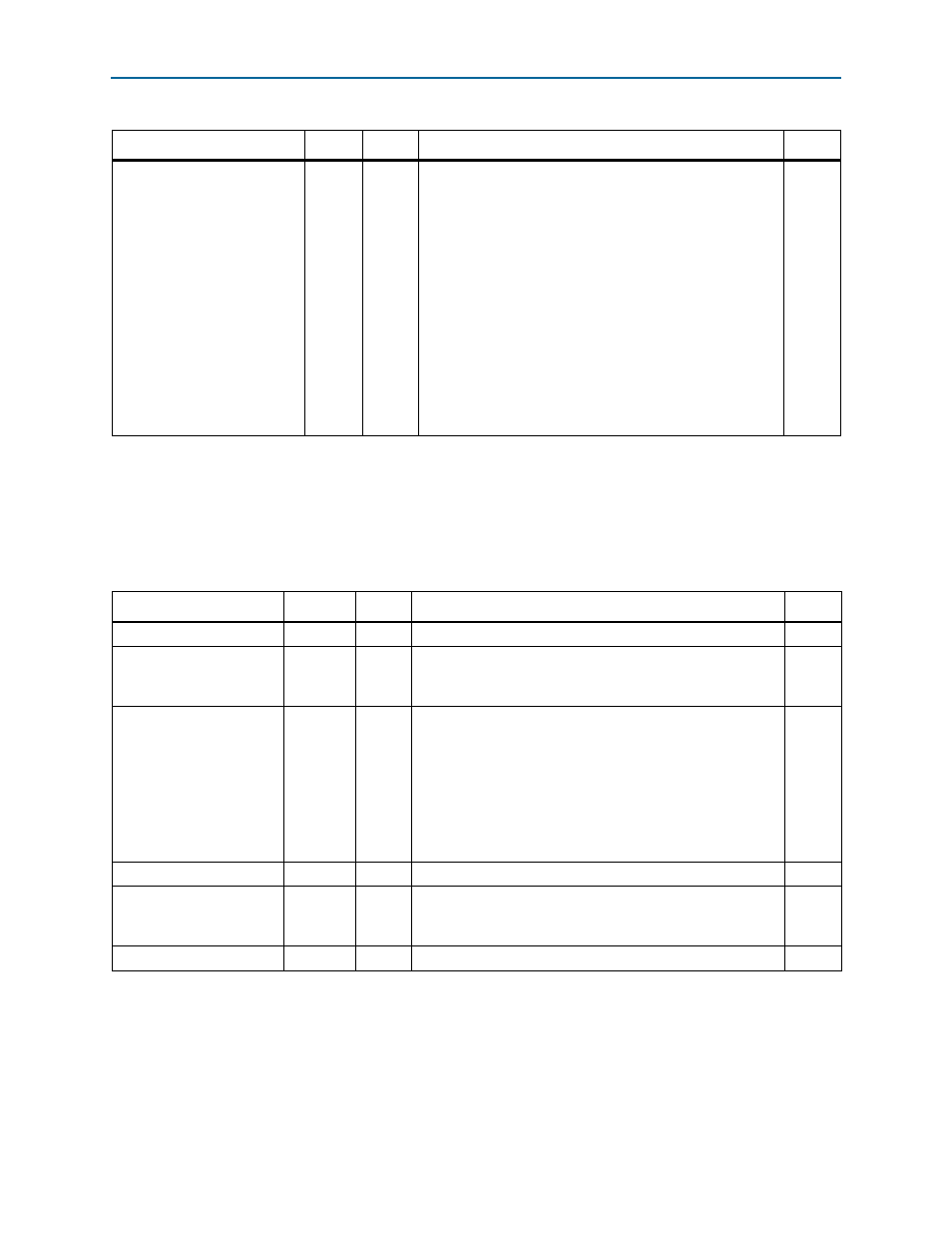

Table 7–29. CPRI_AUTO_CAL— Autocalibration

—Offset: 0x68

Field

Bits

Access Function Default

RSRV

[31:30] UR0

Reserved.

2’h0

cal_pointer

[29:26] RO

Number of autocalibration pipeline stages currently in use.

Each such stage adds one

cpri_clkout

cycle of delay in the

Rx path.

4’h3

cal_status

[25:24] RO

Calibration status. Valid values are:

00: Calibration is turned off

01: Calibration is running or falied with

cal_rtd

value too

low

10: Calibration is running or failed with

cal_rtd

value too

high

11: Calibration is successful

2’h0

RSRV

[23:21] UR0

Reserved.

3’h0

cal_en

[20] RW

Indicates that calibration mode is enabled. When the value in

this field is 1, autocalibration is turned on. When the value in

this field is 0, autocalibration is turned off.

1’h0

cal_rtd

[19:0]

RW

Desired round-trip delay value. Unit is

cpri_clkout

cycles.

20’h0

Notes to

:

(1) CPRI variations with slave clocking mode (CPRI RE slaves) do not support the functionality controlled by this register.

(2) For information about the CPRI IP core autocalibration feature, refer to

“Dynamic Pipelining for Automatic Round-Trip Delay Calibration” on