Table 7–7 – Altera CPRI IP Core User Manual

Page 121

Chapter 7: Software Interface

7–5

CPRI Protocol Interface Registers

December 2013

Altera Corporation

CPRI MegaCore Function

User Guide

operation_mode

[1]

RW

Specifies whether the CPRI IP core is configured with slave clocking

mode or with master clocking mode, according to the following

values:

1’b0—The IP core is in master clocking mode.

1’b1—The IP core is in slave clocking mode.

The initial value of this bit is determined by the value you specify for

the Operation mode parameter in the CPRI parameter editor. When

you modify the value of this bit, you must ensure you connect the

clocks in your design appropriately. Refer to

For information about how to modify the value of this field safely,

refer to

“Dynamically Switching Clock Mode” on page 4–9

.

As

specified

in the

CPRI

parameter

editor

tx_ctrl_insert_en

[0]

RW

Master enable for insertion of control transmit table entries in CPRI

hyperframe. This signal enables control bytes for which the

tx_control_insert

bit is high to be written to the CPRI frame.

1'h0

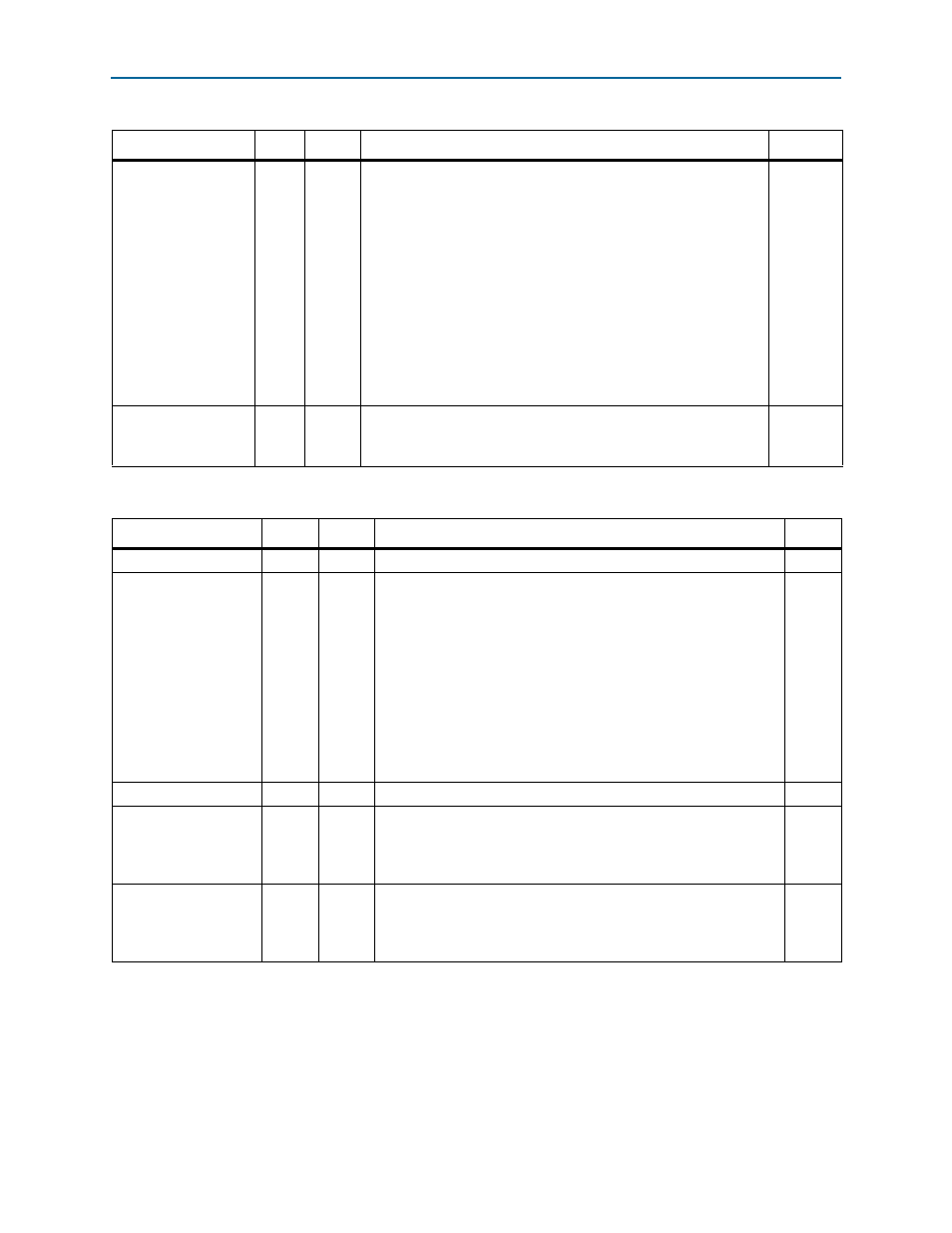

Table 7–6. CPRI_CONFIG—CPRI Configuration—Offset: 0x8 (Part 2 of 2)

Field

Bits

Access

Function

Default

Table 7–7. CPRI_CTRL_INDEX—CPRI Control Word Index—Offset: 0xC

Field

Bits

Access

Function

Default

RSRV

[31:17]

UR0

Reserved.

15'h0

tx_control_insert

[16]

RW

Control word 32-bit section transmit enable. This value is stored in

the control transmit table with its associated entry. When you

change the value of the

cpri_ctrl_index

field, the stored

tx_control_insert

value associated with the indexed entry

appears in the

tx_control_insert

field.

At the time the CPRI IP core can insert a control transmit table entry

in the associated position in the outgoing hyperframe on the CPRI

link, if the

tx_control_insert

bit associated with that entry has

the value of 1, and the

tx_ctrl_insert_en

bit of the

CPRI_CONFIG

register is asserted, the IP core inserts the table entry

in the hyperframe.

1'h0

RSRV

[15:10]

UR0

Reserved.

6'h0

cpri_ctrl_position

[9:8]

RW

Sequence number for CPRI control word 32-bit section monitoring

and insertion. The value in this field determines the 32-bit section of

the control receive and control transmit table entries that appear in

the

CPRI_RX_CTRL

and

CPRI_TX_CTRL

registers.

2'h0

cpri_ctrl_index

[7:0]

RW

Index for CPRI control word monitoring and insertion. The value in

this field determines the control receive and control transmit table

entries that appear in the

CPRI_RX_CTRL

and

CPRI_TX_CTRL

registers.

8'h0