Table 7–50, Table 7–51 – Altera CPRI IP Core User Manual

Page 139

Chapter 7: Software Interface

7–23

Ethernet Registers

December 2013

Altera Corporation

CPRI MegaCore Function

User Guide

1

If you turn off the Include MAC block parameter, your application cannot access the

Ethernet registers. In that case, attempts to access these registers read zeroes and do

not write successfully, as for a Reserved register address.

For more information about these registers, refer to

“Accessing the Ethernet Channel”

.

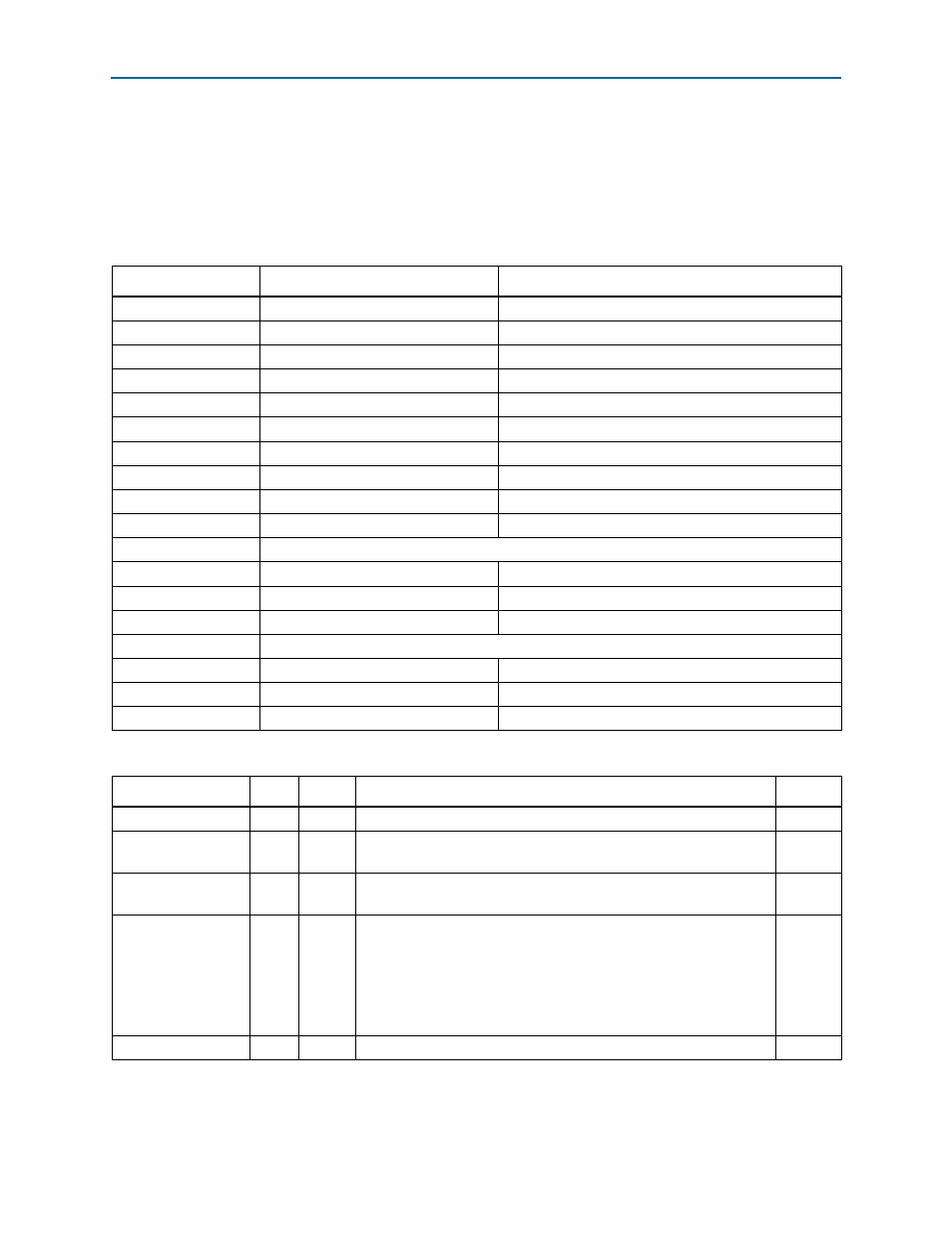

Table 7–50. CPRI Ethernet Registers Memory Map

Address

Name

Expanded Name

0x200

ETH_RX_STATUS

Ethernet Receiver Module Status

0x204

ETH_TX_STATUS

Ethernet Transmitter Module Status

0x208

ETH_CONFIG_1

Ethernet Feature Configuration 1

0x20C

ETH_CONFIG_2

Ethernet Feature Configuration 2

0x210

ETH_RX_CONTROL

Ethernet Rx Control

0x214

ETH_RX_DATA

Ethernet Rx Data

0x218

ETH_RX_DATA_WAIT

Ethernet Rx Data With Wait-State Insertion

0x21C

ETH_TX_CONTROL

Ethernet Tx Control

0x220

ETH_TX_DATA

Ethernet Tx Data

0x224

ETH_TX_DATA_WAIT

Ethernet Tx Data With Wait-State Insertion

0x228

Reserved

0x22C

ETH_MAC_ADDR_MSB

Ethernet MAC Address MSB (16 bits)

0x230

ETH_MAC_ADDR_LSB

Ethernet MAC Address LSB (32 bits)

0x234

ETH_HASH_TABLE

Ethernet Multicast Filtering Hash Table

0x238–0x240

Reserved

0x244

ETH_FWD_CONFIG

Ethernet Forwarding Configuration

0x248

ETH_CNT_RX_FRAME

Ethernet Receiver Module Frame Counter

0x24C

ETH_CNT_TX_FRAME

Ethernet Transmitter Module Frame Counter

Table 7–51. ETH_RX_STATUS—Ethernet Receiver Module Status—Offset: 0x200 (Part 1 of 2)

Field

Bits

Access

Function

Default

RSRV

[31:7] UR0

Reserved.

25'h0

rx_ready_block

[6]

RO

Indicates that an 8-word block of Ethernet data is available to be

transmitted on the Ethernet channel.

1’h0

rx_ready_end

[5]

RO

Indicates the end-of-packet (EOP) is available in the Ethernet Rx

buffer, ready to be transmitted on the Ethernet channel.

1’h0

rx_length

[4:3]

RO

Length of the final word in the packet. Values are:

00: 1 valid byte

01: 2 valid bytes

10: 3 valid bytes

11: 4 valid bytes

2’h0

rx_abort

[2]

RO

Indicates the current Ethernet Rx packet is aborted.

1’h0