Rx frame offset, Offs – Altera CPRI IP Core User Manual

Page 135

Chapter 7: Software Interface

7–19

MAP Interface and AUX Interface Configuration Registers

December 2013

Altera Corporation

CPRI MegaCore Function

User Guide

map_rx_offset_x

[7:0]

RW

Basic frame number for start of MAP receiver AxC container block

write to each enabled mapN Rx buffer.

8’h0

Notes to

:

(1) In synchronous buffer mode, the offset specified in this register must precede (be less than) the offset specified in the

CPRI_START_OFFSET_RX

register described in

. For an explanation of this requirement and an overview of the considerations in determining the value in this

register, refer to

“MAP Receiver in Synchronous Buffer Mode” on page 4–21

and to

. If your register values do not

comply with this requirement, your CPRI IP core will experience data corruption on the active data channels in the synchronous buffer

synchronization mode.

(2) This register does not participate in data transfer synchronization on the antenna-carrier interfaces in FIFO mode.

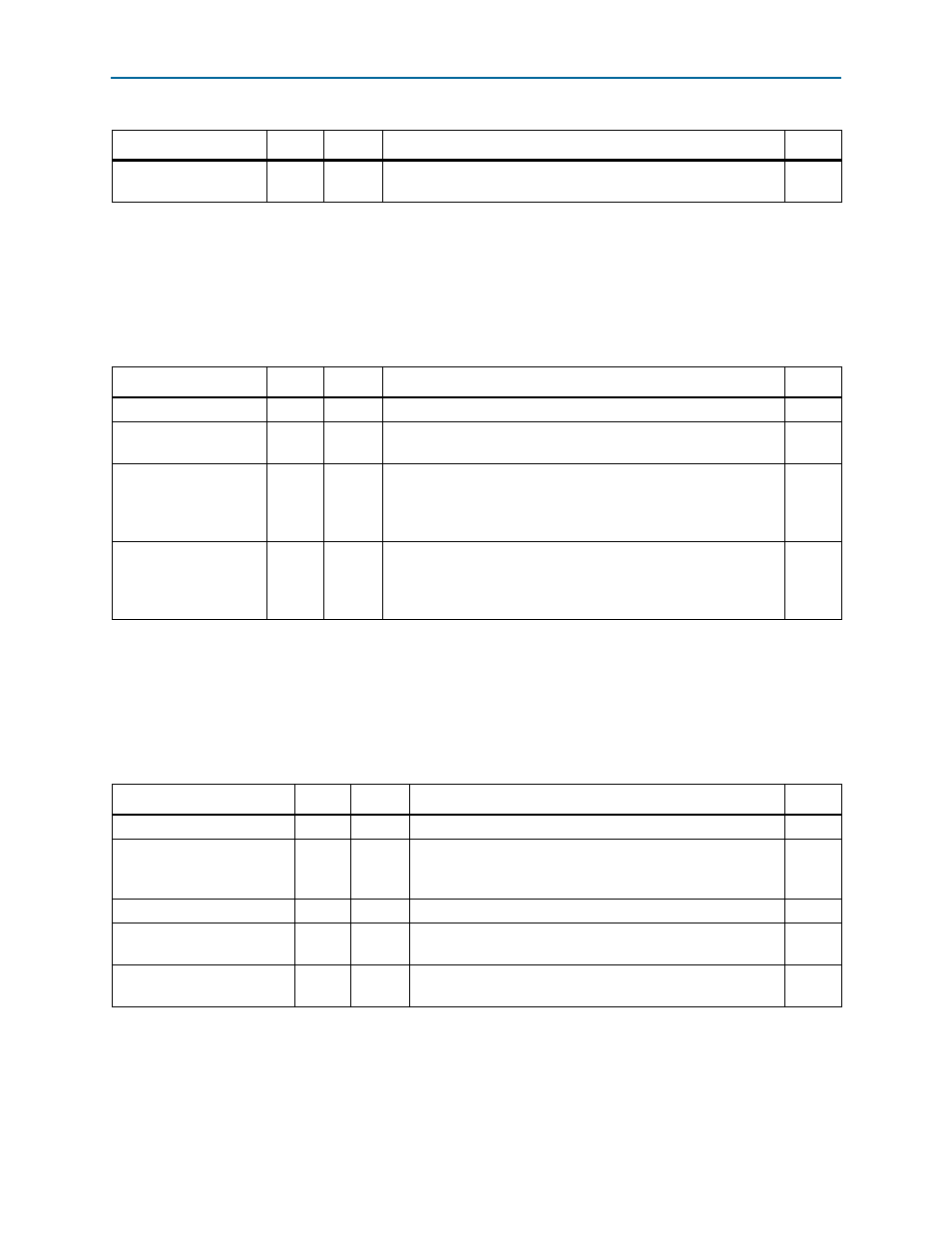

Table 7–37. CPRI_MAP_OFFSET_RX—MAP Rx Frame Offset

(1)

,

(2)

—Offset: 0x118 (Part 2 of 2)

Field

Bits

Access

Function

Default

Table 7–38. CPRI_MAP_OFFSET_TX—MAP Tx Frame Offset

,

—Offset: 0x11C

Field

Bits

Access

Function

Default

RSRV

[31:17] UR0

Reserved.

15'h0

map_tx_hf_resync

[16]

RW

Enables synchronization every hyperframe instead of every radio

frame. When asserted, the

map_tx_offset_z

field is ignored.

1’h0

map_tx_offset_z

[15:8]

RW

Hyperframe number for start of read of MAP transmitter AxC

container block from each enabled mapN Tx buffer. The CPRI IP

core reads the data from the mapN Tx buffer and routes it to the

CPRI frame buffer to be prepared for transmission on the CPRI link.

8’h0

map_tx_offset_x

[7:0]

RW

Basic frame number for start of read of MAP transmitter AxC

container block from each enabled mapN Tx buffer. The CPRI IP

core reads the data from the mapN Tx buffer and routes it to the

CPRI frame buffer to be prepared for transmission on the CPRI link.

8’h0

Notes to

:

(1) In synchronous buffer mode, the offset specified in this register must follow (be greater than) the offset specified in the

CPRI_START_OFFSET_TX

register described in

. For an explanation of this requirement and an overview of the considerations in

determining the value in this register, refer to

“MAP Transmitter in Synchronous Buffer Mode” on page 4–27

. If your register values do not comply with this requirement, your CPRI IP core will experience data corruption on the active data

channels in the synchronous buffer synchronization mode.

(2) This register does not participate in data transfer synchronization on the antenna-carrier interfaces in FIFO mode.

Table 7–39. CPRI_START_OFFSET_RX—Rx Start Frame Offset

,

—Offset: 0x120 (Part 1 of 2)

Field

Bits

Access

Function

Default

RSRV

[31:25] UR0

Reserved.

7'h0

start_rx_hf_resync

[24]

RW

Enables synchronization every hyperframe instead of every

radio frame. When asserted, the

start_rx_offset_z

field is

ignored.

1’h0

RSRV

[23:22] UR0

Reserved.

2'h0

start_rx_offset_seq

[21:16] RW

Sequence number for start of

cpri_rx_start

synchronization output.

6’h0

start_rx_offset_z

[15:8]

RW

Hyperframe number for start of

cpri_rx_start

synchronization output.

8’h0