Clocking structure, Cpri ip core clocks, Clocking structure –3 – Altera CPRI IP Core User Manual

Page 35: Cpri ip core clocks –3

Chapter 4: Functional Description

4–3

Clocking Structure

December 2013

Altera Corporation

CPRI MegaCore Function

User Guide

Clocking Structure

The CPRI IP core has a variable number of clock domains. The clock domains in your

CPRI IP core variation depend on the following factors:

■

Number of antenna-carrier interfaces.

■

Whether the MII is configured.

■

Whether the antenna-carrier interfaces are clocked internally. Refer to

Internally-Clocked Synchronization Mode” on page 3–7

■

Target device family.

■

In one case, different CPRI line rates.

The input clock frequency requirements depend on the target device family and CPRI

line rate. Refer to

Table 4–2 on page 4–10

for these requirements.

You can configure a CPRI IP core in master or slave clocking mode, as described in

“Operation Mode Parameter” on page 3–2

. REC configurations and RE master

configurations use master clocking mode, and RE slave configurations use slave

clocking mode. Your design must handle some of the transceiver input clocks

differently in the two different clocking modes. The clocking diagrams in

Diagrams for the CPRI IP Core” on page 4–5

describe the requirements.

The CPRI IP core supports dynamic switching between master and slave clocking

modes in Arria V, Cyclone V, and Stratix V devices. This section describes how to

connect the CPRI IP core input clock signals to support dynamic clock mode

switching and how to dynamically switch the clock mode in your CPRI IP core.

Table 4–1

describes the individual clocks. The clocking diagrams in

show the clocks and clock domain boundaries.

Table 4–2 on page 4–10

lists the clock frequencies for the different CPRI IP core

variations.

CPRI IP Core Clocks

Table 4–1

describes the clock domains in the CPRI IP core.

For more information about these clocks, including driver requirements, refer to

. For expected input clock frequencies refer to

and to

Table 4–2 on page 4–10

.

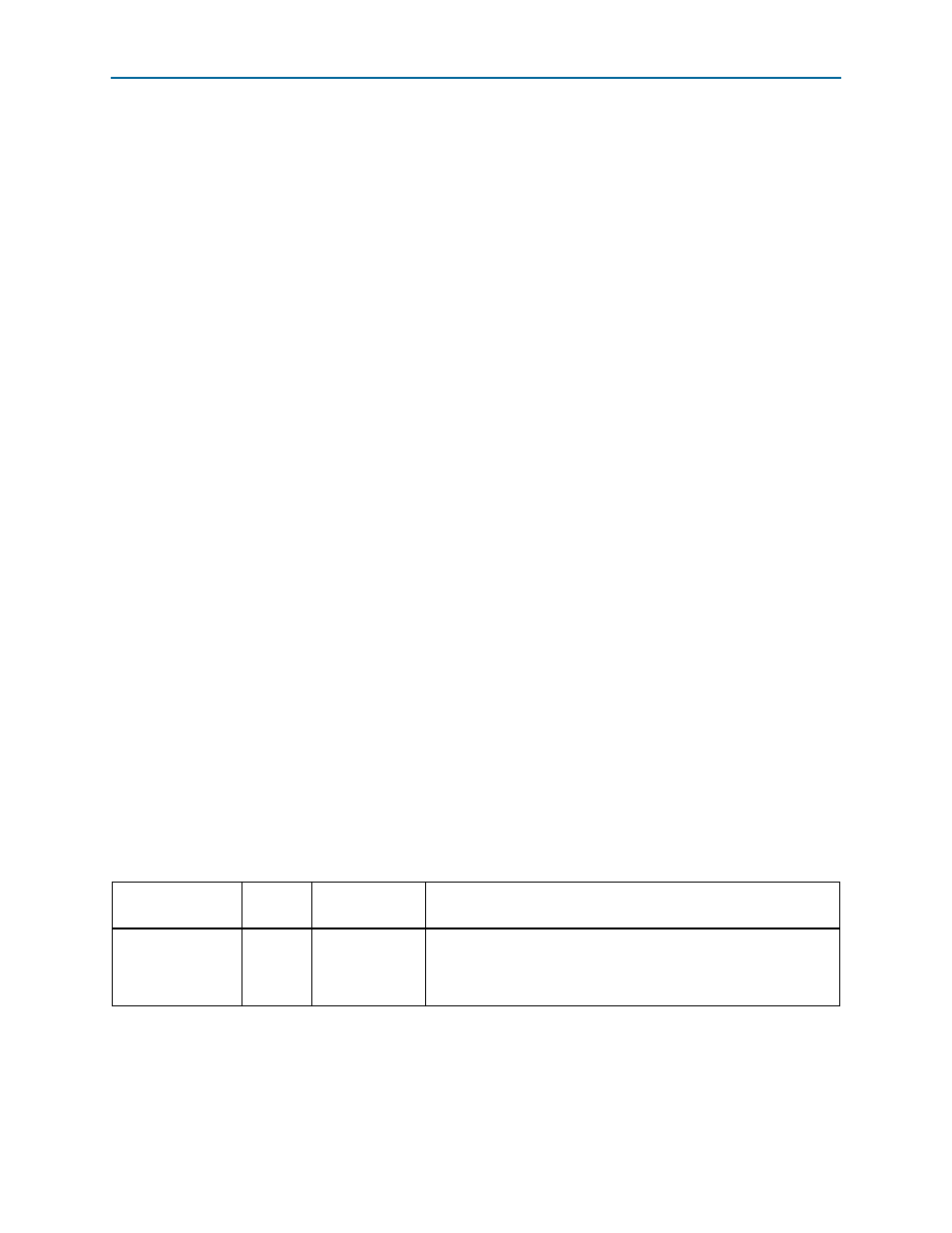

Table 4–1. CPRI IP Core Clocks (Part 1 of 3)

Clock Name

Direction

Configuration

Requirements

Description

cpri_clkout

Output

Present in all

CPRI IP cores

Main clock for the CPRI IP core. The CPRI IP core derives this clock

from the transceiver transmit PLL, and the frequency of this clock

depends on the CPRI line rate. For more information refer to

Communication Link Line Rates” on page 4–10

.