Altera CPRI IP Core User Manual

Page 208

F–2

Appendix F: Integrating the CPRI IP Core Timing Constraints in the Full Design

CPRI MegaCore Function

December 2013

Altera Corporation

User Guide

set_false_path -from * -to *sync

set_false_path -from * -to *sync[*]

set_false_path -from * -to *sync1

set_false_path -from * -to *sync1[*]

set_false_path -from * -to *s0

set_false_path -from * -to *s0[*]

create_generated_clock -name txclk_div2 -source [get_pins -compatibility_mode

*transmit_pcs0|clkout] -divide_by 2 [get_registers *txclk_div2]

derive_clock_uncertainty

set_clock_groups -exclusive -group txclk_div2 -group *receive_pcs0|clkout

set_clock_groups -exclusive -group *transmit_pcs0|clkout -group

*receive_pcs0|clkout

set_clock_groups -asynchronous -group cpu_clk -group txclk_div2

set_clock_groups -asynchronous -group map*_clk -group txclk_div2

set_clock_groups -asynchronous -group clk_ex_delay -group {txclk_div2

*transmit_pcs0|clkout *receive_pcs0|clkout}

set_clock_groups -asynchronous -group reconfig_clk -group txclk_div2

When you embed your CPRI IP core variation in your full design, you drive the CPRI

IP core clocks directly from the top-level signals of the design or indirectly through

internal logic. The timing constraints for your full design must reference the clock

names relative to the full design hierarchy.

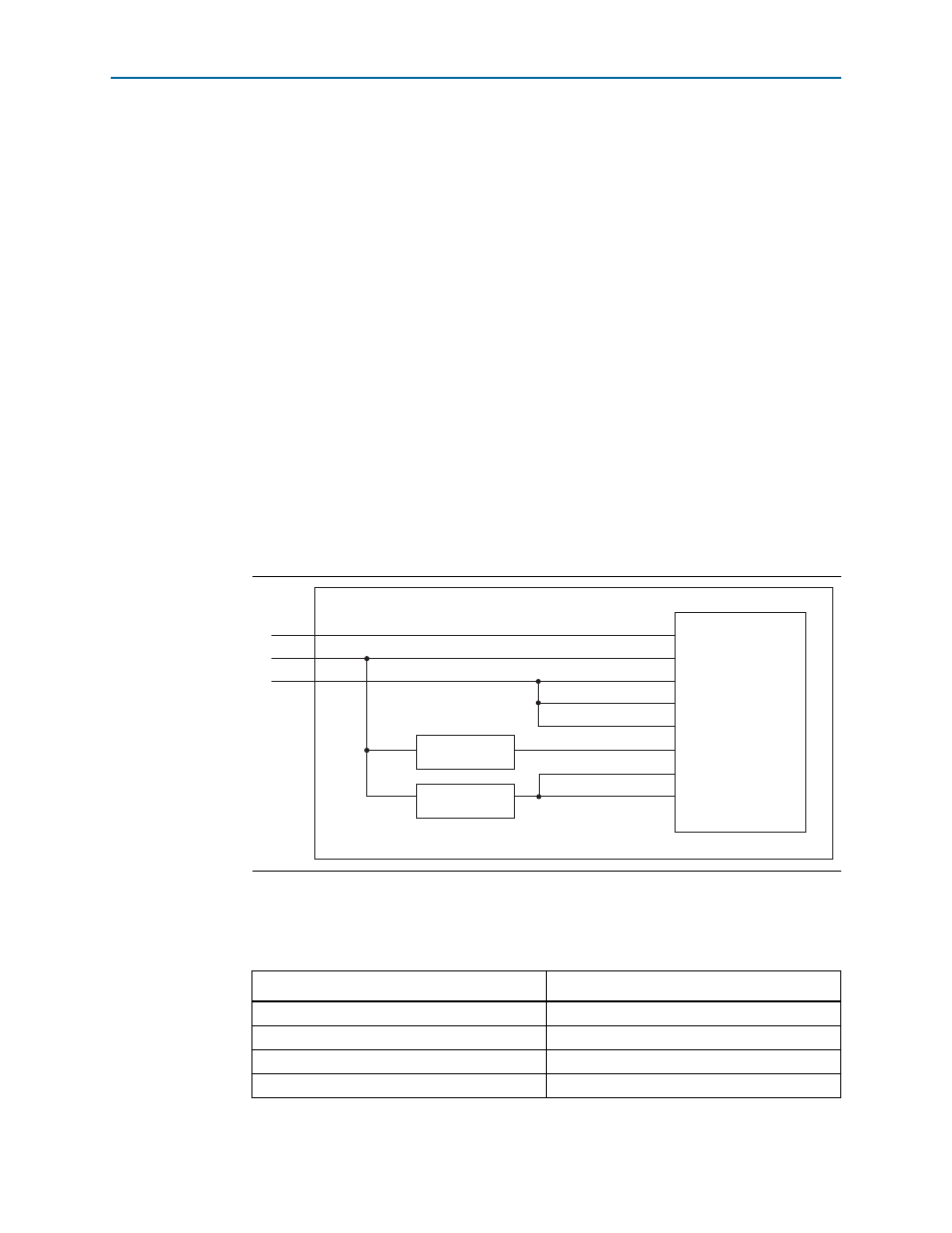

shows an example design that contains the example CPRI IP core

variation.

lists the correspondence between the clock names in the .sdc file and the

signal names in the full design.

Figure F–1. Clocks Driving CPRI IP Core Clocks in Example Full Design

Table F–1. Stand-Alone IP Core Clock Names and Example Design Clock Names (Part 1 of 2)

Stand-Alone IP Core Clock Name

Full Design Clock Name

gxb_refclk

cpri_ref_clk

gxb_pll_inclk

cleaned_clkin

gxb_cal_blk_clk

clkin_50mhz

reconfig_clk

clkin_50mhz

gxb_refclk

CPRI IP Core

cpri_ref_clk

gxb_pll_inclk

gxb_cal_blk_clk

reconfig_clk

cpu_clk

clk_ex_delay

map0_tx_clk

map0_rx_clk

cleaned_clkin

clkin_50mhz

PLL2

PLL1

cpri_0_inst