Altera CPRI IP Core User Manual

Page 183

Appendix E: Delay Measurement and Calibration

E–5

Single-Hop Delay Measurement

December 2013

Altera Corporation

CPRI MegaCore Function

User Guide

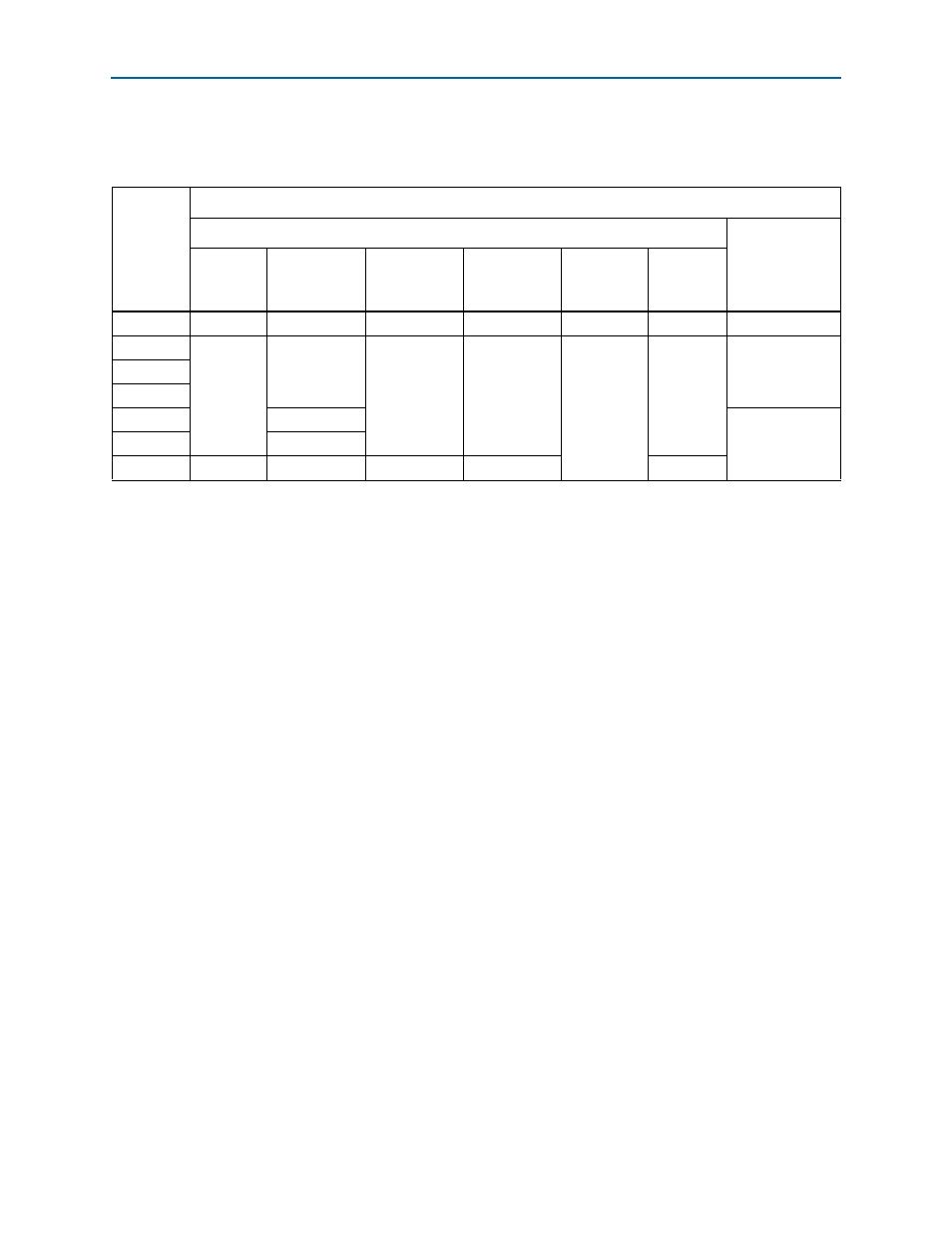

Table E–1

shows the fixed latency through the transceiver in the receive side of the

CPRI IP core.

The clean-up PLLs shown in

use the recovered clock as input to the PLL that generates the

gxb_pll_inclk

signal (and the

usr_clk

and

usr_pma_clk

signals in

), to

ensure frequency match. To preserve the

T_txv_RX

latencies listed in

Table E–1

,

you must ensure that the reference clock to the clean-up PLL contains no

asynchronous dividers.

Table E–1. Fixed Latency T_txv_RX Through Rx Transceiver in CPRI IP Core

CPRI Line

Rate

(Gbps)

Latency Through Transceiver in cpri_clkout Clock Cycles

CPRI IP Core Variations with Hard PCS

Soft PCS

Variations on

Arria V GT

Device

(11)

Arria II GX

Device

(1)

Cyclone IV GX

Device

(1)

Arria II GZ or

Stratix IV GX

Device

(1)

Arria V

(GX or GT

(5)

)

Device

Arria V GZ

or Stratix V

Device

Cyclone V,

Device

0.6144

2.6

(2)

2.6

(2)

2.6

(2)

2.85

2.65

3.149

—

1.2288

5.7

(3)

5.7

(3)

7.2

(4)

8.224

6.782

(10)

8.774

(7)

9.724

2.4576

3.072

4.9152

—

23.98

6.144

—

9.8304

—

—

—

—

(9)

,

—

,

Notes to

Table E–1

:

(1) Latency numbers for Arria II GX, Arria II GZ, Cyclone IV GX, and Stratix IV GX devices are accurate when the

rx_bitslipboundaryselectout

field of the

CPRI_TX_BITSLIP

register has the value of zero, For the appropriate full formula to calculate

the value of T_txv_RX in other cases, refer to Notes

(2)

,

(3)

, and

(4)

and where they are referenced in the table.

(2) In this case,

T_txv_RX

= (100 + (4 +

rx_bitslipboundaryselectout

))/40, where

rx_bitslipboundaryselectout

is the value in this

field in the

CPRI_TX_BITSLIP

register.

(3) In this case,

T_txv_RX

= (220 + (8 –

rx_bitslipboundaryselectout

))/40, where

rx_bitslipboundaryselectout

is the value in this

field in the

CPRI_TX_BITSLIP

register.

(4) In this case,

T_txv_RX

= (280 + (8 –

rx_bitslipboundaryselectout

))/40, where

rx_bitslipboundaryselectout

is the value in this

field in the

CPRI_TX_BITSLIP

register. If the

rx_byte_delay

field of the

CPRI_RX_DELAY

register has a non-zero value, the delay is 6.7

cpri_clkout

cycles instead of 7.2.

(5) If you configure your CPRI IP core with the CPRI line rate of 9.8304 Gbps, and target an Arria V GT device, the IP core is configured with a soft

PCS. The soft PCS configuration does not change with autorate negotiation to a lower frequency. This column describes variations that are not

configured with a soft PCS.

(6) If the

rx_byte_delay

field of the

CPRI_RX_DELAY

register has a non-zero value, this delay is 7.724

cpri_clkout

cycles instead of 8.224

cpri_clkout

cycles.

(7) If the

rx_byte_delay

field of the

CPRI_RX_DELAY

register has a non-zero value, this delay is 8.274

cpri_clkout

cycles instead of 8.774

cpri_clkout

cycles.

(8) f the

rx_byte_delay

field of the

CPRI_RX_DELAY

register has a non-zero value, this delay is 9.224

cpri_clkout

cycles instead of 9.724

cpri_clkout

cycles.

(9) Arria V GX devices do not support a CPRI IP core line rate of 9.8304 Gbps. Arria V GT devices support a CPRI IP core line rate of 9.8304 Gbps

only in soft PCS variations.

(10) If the

rx_byte_delay

field of the

CPRI_RX_DELAY

register has a non-zero value, the delay is 6.282

cpri_clkout

cycles instead of 6.782.

(11) The values described in this column apply to all Arria V GT variations that are configured with a CPRI line rate of 9.8304 Gbps, even after

autorate negotiation to a lower frequency. These variations cannot auto-negotiate to a CPRI line rate of 0.6144 Gbps.