Cpri protocol interface layer (physical layer), Cpri protocol interface layer (physical layer) –51 – Altera CPRI IP Core User Manual

Page 83

Chapter 4: Functional Description

4–51

CPRI Protocol Interface Layer (Physical Layer)

December 2013

Altera Corporation

CPRI MegaCore Function

User Guide

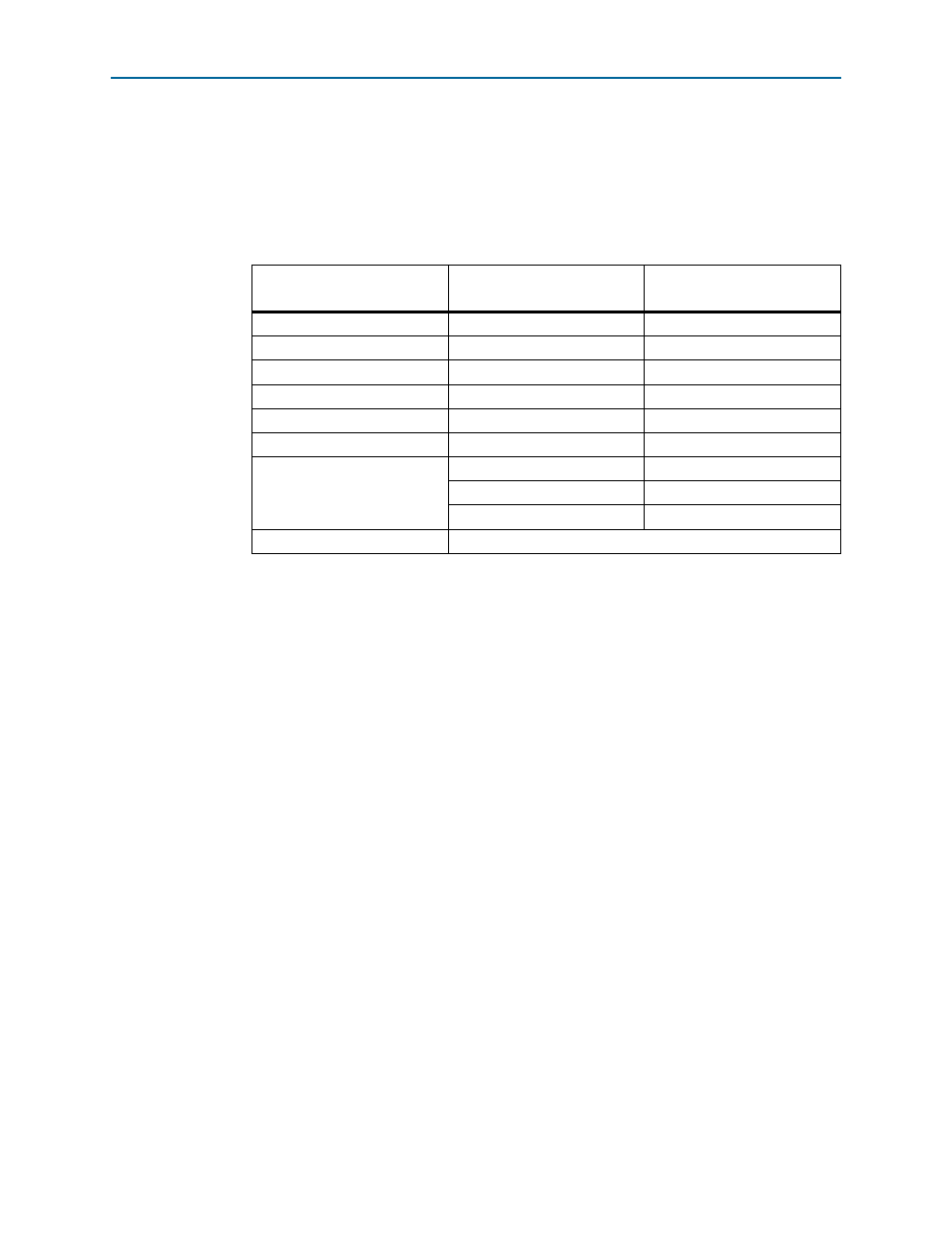

In the CPRI IP core, the HDLC block, or slow data link layer, passes HDLC data

between the CPU interface and the CPRI receiver and transmitter interfaces to the

CPRI link. The CPRI specification dictates that the HDLC channel rate is specified in

the three lowest bits of control byte Z.66.0. The value 3’b000 indicates that no HDLC

channel is supported in the current hyperframe.

shows the possible rate

configurations.

The HDLC channel rate is determined during the software set-up sequence or by

dynamic modification, in which the same new pointer value is received in CPRI

control byte Z.66.0 four hyperframes in a row. The accepted receive rate is specified in

the

rx_slow_cm_rate

field of the

CPRI_CM_STATUS

register, and the transmit rate is

specified in the

tx_slow_cm_rate

field of the

CPRI_CM_CONFIG

register.

The CPU interface control for the HDLC channel is identical to the CPU interface

control for the Ethernet channel, with the following exceptions:

■

HDLC register names replace

ETH

with

HDLC

■

HDLC channel control has fewer configurations than the Ethernet channel control

■

HDLC channel control does not support address filtering

1

The CPRI IP core implements the CRCDT CRC-16 allowed by the HDLC specification,

rather than the CRC-32.

CPRI Protocol Interface Layer (Physical Layer)

The physical layer of the CPRI protocol is also called layer 1. This layer controls the

electrical characteristics of the CPRI link, the time-division multiplexing of the

separate information flows in the protocol, and low-level signaling. The CPRI

protocol interface module of the CPRI IP core incorporates Altera’s high-speed

transceivers to implement layer 1. The transceivers are configured in deterministic

latency mode, supporting the extended delay measurement requirements of the CPRI

specification.

Table 4–15. HDLC Channel Bit Rates

Value in Z.66.0.0[2:0]

HDLC Bit Rate

(Kbps)

Minimum CPRI Line Rate

(Mbps)

000

—

614.4

001

240

614.4

010

480

614.4

011

960

1228.8

100

1920

2457.6

101

2400

3072.0

110

3840

4915.2

4800

6144.0

7680

9830.4

111

Note to

(1) When Z.66.0.0[2:0] holds value 3’b111, the HDLC bit rate is the highest HDLC bit rate possible for the current CPRI

line rate. You can derive that bit rate from the other entries in this table.