Altera CPRI IP Core User Manual

Page 106

6–8

Chapter 6: Signals

Auxiliary Interface Signals

CPRI MegaCore Function

December 2013

Altera Corporation

User Guide

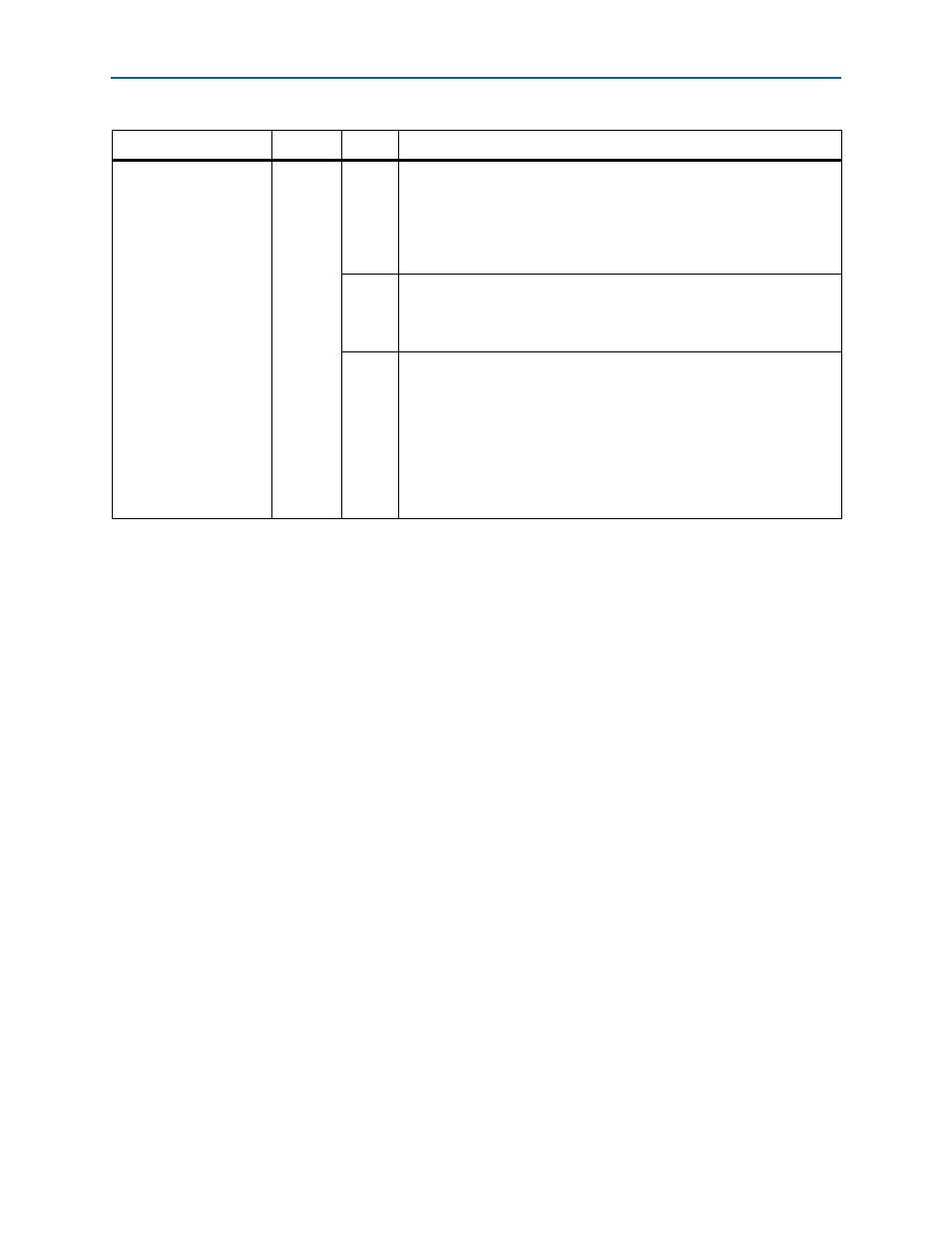

aux_tx_mask_data

[64:0]

Input

[64]

cpri_tx_sync_rfp

: Synchronization input used in REC master to control

the start of a new 10 ms radio frame. Asserting this signal resets the frame

synchronization machine. The CPRI IP core uses the rising edge of the

pulse for synchronization. For information about the CPRI IP core

response to a pulse on this signal, refer to

and

surrounding text.

[63:32]

cpri_tx_aux_data

: Data received on the AUX link, aligned with

cpri_tx_seq

with a delay of two

cpri_clkout

cycles. Data is

transmitted in 32-bit words. Byte [31:24] is transmitted first, and byte

[7:0] is transmitted last.

[31:0]

cpri_tx_aux_mask

: Bit mask for insertion of data from

cpri_tx_aux_data

in the outgoing CPRI frame. Assertion of a bit in this

mask overrides insertion of data to the corresponding bit in the outgoing

CPRI frame from any other source. Therefore, the mask bits must be

deasserted during K28.5 character insertion in the outgoing CPRI frame,

which occurs when Z=X=0. If you do not deassert the mask bits during

K28.5 character insertion in the outgoing CPRI frame, the

cpri_tx_error

output signal is asserted in the following

cpri_clkout

cycle.

Table 6–4. AUX Transmitter Interface Signals (Part 2 of 2)

Signal

Direction

Bits

Description