Calculation example: rx buffer delay – Altera CPRI IP Core User Manual

Page 186

E–8

Appendix E: Delay Measurement and Calibration

Single-Hop Delay Measurement

CPRI MegaCore Function

December 2013

Altera Corporation

User Guide

Calculation Example: Rx Buffer Delay

This section walks you through an example that shows you how to calculate the

frequency at which to run

clk_ex_delay

, and how to program and use the registers to

determine the delay through the CPRI Receive buffer.

For example, assume your CPRI IP core runs at data rate 3072 Mbps. In this case,

shows that the

cpri_clkout

frequency is 76.80 MHz, so a

cpri_clkout

cycle is 1/(76.80 MHz).

Refer to

Table E–2

for the accuracy resolution provided by some sample M/N ratios.

If your accuracy resolution requirements are satisfied by an M/N ratio of 128/127,

perform the following steps:

1. Program the value N=127 in the

ex_delay

field of the

CPRI_EX_DELAY_CONFIG

register at offset 0x3C (

).

2. Perform the following calculation to determine the

clk_ex_delay

frequency that

supports your desired accuracy resolution:

clk_ex_delay

period = (M/N)

cpri_clkout

period

= (128/127) (1/(76.80 MHz))

= (128/127)(13.02083 ns)

= 13.123356 ns

Based on this calculation, the frequency of

clk_ex_delay

is

1/(13.123356 ns) = 76.20 MHz

The following steps assume that you run

clk_ex_delay

at this frequency.

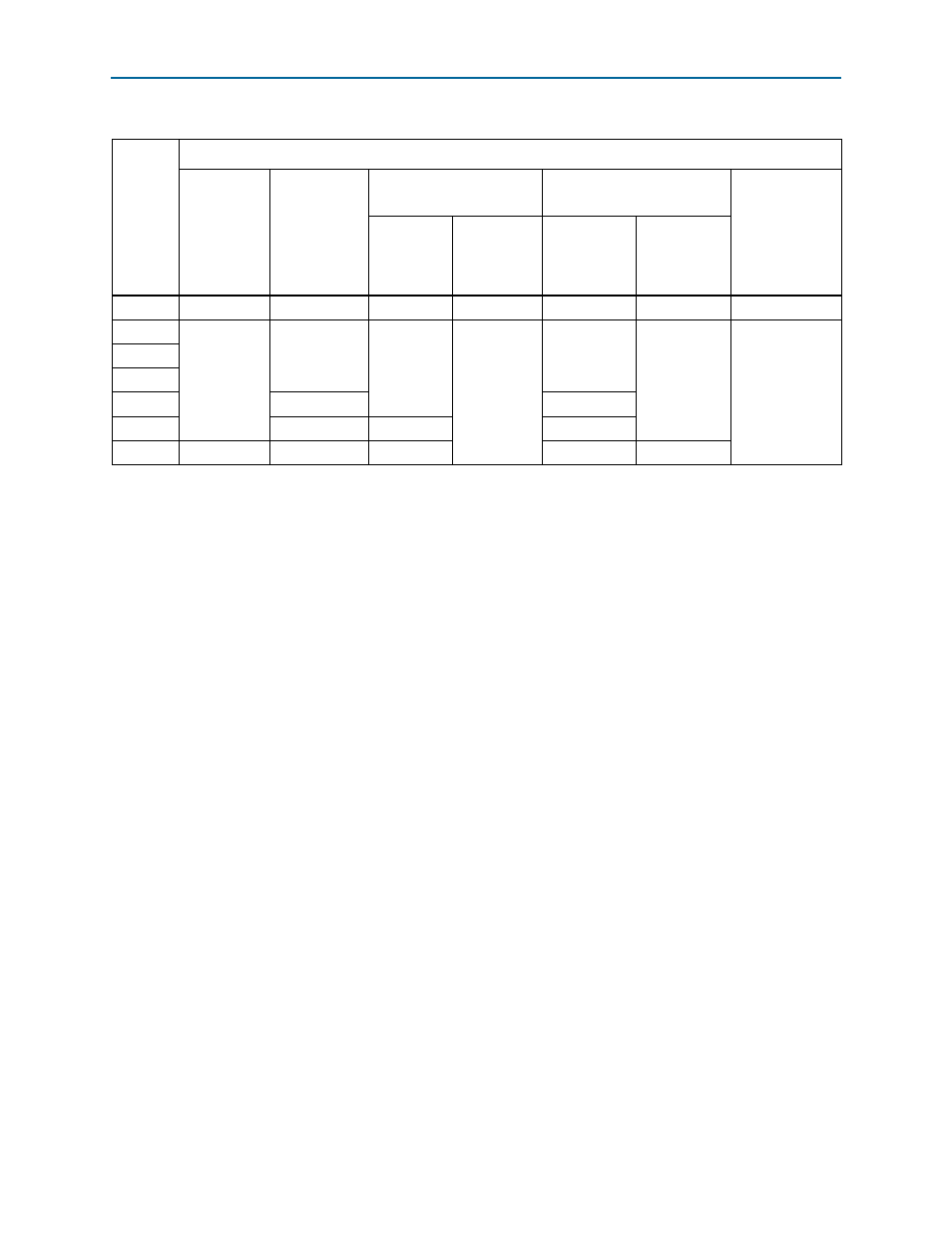

Table E–3. Fixed Latency T_R1 in cpri_clkout Cycles

CPRI

Line

Rate

(Gbps)

Latency Through Core on Rx Path in cpri_clkout Clock Cycles

Arria II GX,

Arria II GZ,

or

Stratix IV GX

Device

Cyclone IV GX

or Cyclone V

Device

Stratix V or Arria V GZ

Device

Arria V GX or Arria V GT

Device

Arria V GT

Device

Configured at

9.8304 Gbps

Configured

at 4.9152

Gbps or

Slower

Configured

at 6.144 or

9.8304 Gbps

Configured

at 3.072

Gbps or

Slower

Configured

at 4.9152 or

6.144 Gbps

0.6144

3.5

3.5

3.5

4.5

3.5

4.5

—

1.2288

5

5

5

5

5

6

(2)

4

2.4576

3.072

4.9152

—

—

6.144

—

—

—

9.8304

—

—

—

—

—

Notes to

Table E–3

:

(1) In the Quartus II software release v13.1, v13.0 SP1, and v13.0, and in the releases that precede release v12.1, the fixed latency T_R1 in this

case is five cpri_clkout cycles. However, in the Quartus II software releases v12.1 and v12.1 SP1, the fixed latency T_R1 in this case is six

cpri_clkout cycles.

(2) In the Quartus II software releases v12.1 and later, the fixed latency T_R1 in this case is six cpri_clkout cycles. However, in the Quartus II

software releases that precede release v12.1, the fixed latency T_R1 in this case is five cpri_clkout cycles.