Map receiver in synchronous buffer mode, Map receiver in synchronous buffer mode –21 – Altera CPRI IP Core User Manual

Page 53

Chapter 4: Functional Description

4–21

MAP Interface

December 2013

Altera Corporation

CPRI MegaCore Function

User Guide

is not yet asserted, the mapN Rx buffer continues to fill. When it overflows, the new

data overwrites current data in the mapN Rx buffer. Each mapN Rx buffer is

implemented as a circular buffer, so the data is overwritten starting at the current

head of the mapN Rx buffer, that is, starting from the initial data not yet sent out on

the data channel.

FIFO-based communication is simple but does not allow easy control of buffer delay.

The delay through each mapN Rx buffer depends on your programmed threshold

value and the application. Data is not sent to a data channel before the buffer

threshold is reached, so the delay through the buffer depends on the fill level. Each

AxC interface has the same buffer threshold, but each Rx buffer reaches that threshold

independently.

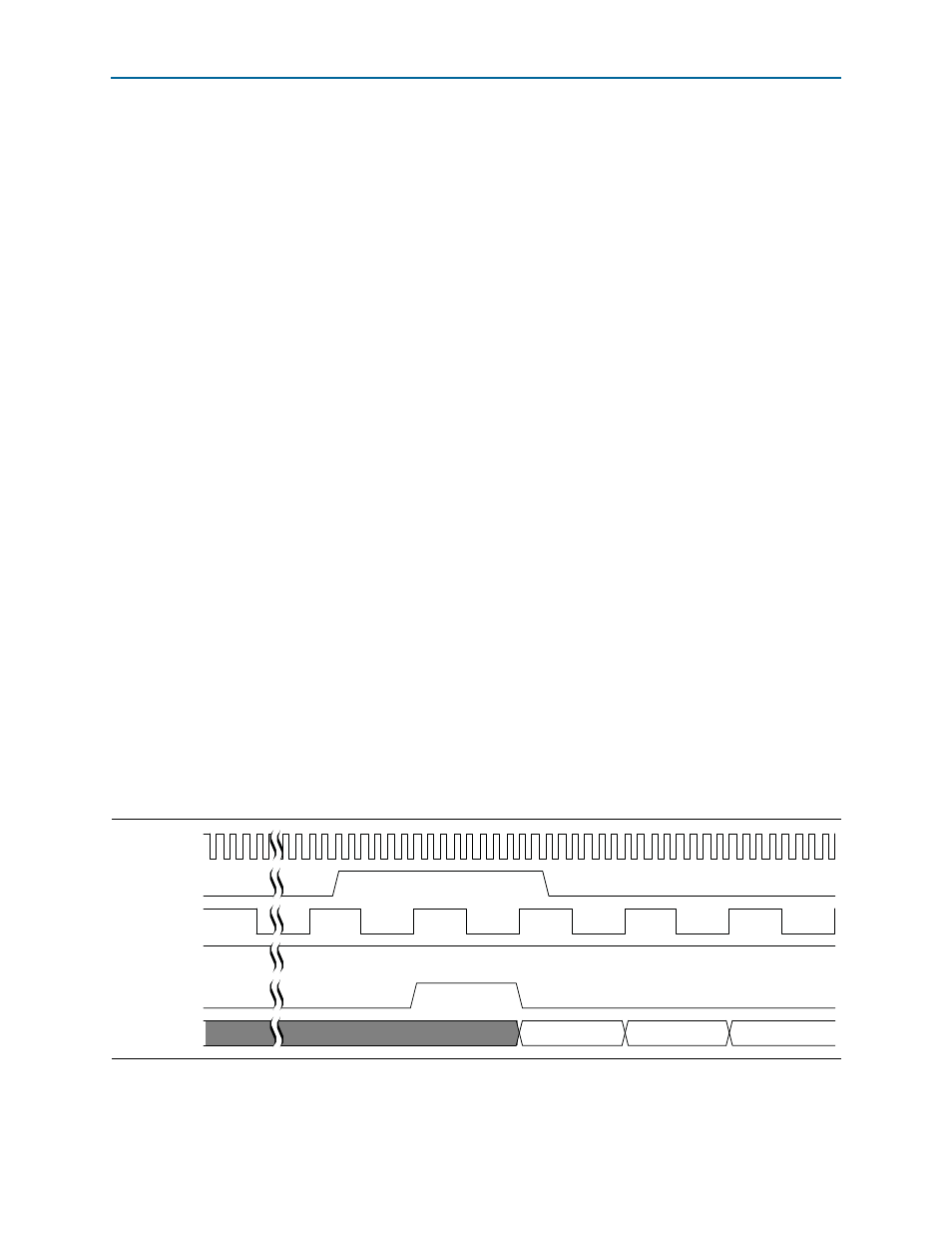

MAP Receiver in Synchronous Buffer Mode

In synchronous buffer mode, each AxC interface has a resynchronization signal,

mapN_rx_resync

. The application that controls the data channel asserts its

resynchronization signal synchronously with the

mapN_rx_clk

clock. After the

application asserts the resynchronization signal, it begins reading data on the

mapN_rx_data[31:0]

data bus for the individual AxC interface.

In synchronous buffer mode, the application should ignore the

mapN_rx_valid

output

signals and hold the

mapN_rx_ready

input signals high. The CPRI IP core does assert

the

mapN_rx_valid

output signals in response to the

mapN_rx_ready

signals. If the

application does not hold the

mapN_rx_ready

input signals high, the CPRI IP core

MAP Rx interface does not function correctly.

For details about the behavior of the individual signals in synchronous buffer mode,

refer to

“MAP Receiver Signals” on page 6–1

.

shows the behavior of the MAP Rx signals in synchronous buffer mode.

In this example, the CPRI line rate is 2457.6 Mbps. The

cpri_rx_start

signal is

asserted for the duration of a single frame, and the CPRI line rate determines the

duration of a basic frame in

cpri_clkout

cycles. At 2457.6 Mbps, a basic frame is 16

cpri_clkout

cycles. At this line rate, as shown in

Table 4–2 on page 4–10

, the

cpri_clkout

frequency is 61.44 MHz. The

mapN_rx_clk

frequency is 7.68 MHz

(oversampling rate 2), approximately 0.125 times the

cpri_clkout

frequency.

Figure 4–10. MAP Receiver Interface in Synchronous Buffer Mode

cpri_clkout

cpri_rx_start

mapN_rx_clk

mapN_rx_ready

mapN_rx_resync

mapN_rx_data[31:0]