Running the autorate negotiation testbench – Altera CPRI IP Core User Manual

Page 167

Appendix C: CPRI Autorate Negotiation Testbench

C–5

Running the Autorate Negotiation Testbench

December 2013

Altera Corporation

CPRI MegaCore Function

User Guide

Running the Autorate Negotiation Testbench

To run the CPRI IP core autorate negotiation testbench, perform the following steps:

1. In the Quartus II software, create a project using the New Project Wizard on the

File menu. Name the project cpri_top_level. If you change this name you must edit

the testbench simulation .tcl file. The project targets the same device as your

intended DUT. Refer to

Table C–3

.

2. Generate the CPRI IP core initial variation with the properties shown in

Table C–3

.

For all 28-nm device variations (the autorate negotiation testbenches for which

you deliberately simulate the DUT with the wrong example design files to force

the DUT to perform autorate negotiation), when you are prompted to generate an

example design, you must turn on Generate Example Design and click Generate.

1

For the Stratix IV GX and Cyclone IV GX autorate negotiation testbenches,

turn off Generate Example Design before you click Generate. The initial

variation you generate is not the variation with which you run the

testbench. For these two testbenches, you run simulation with the example

design that you generate together with the DUT.

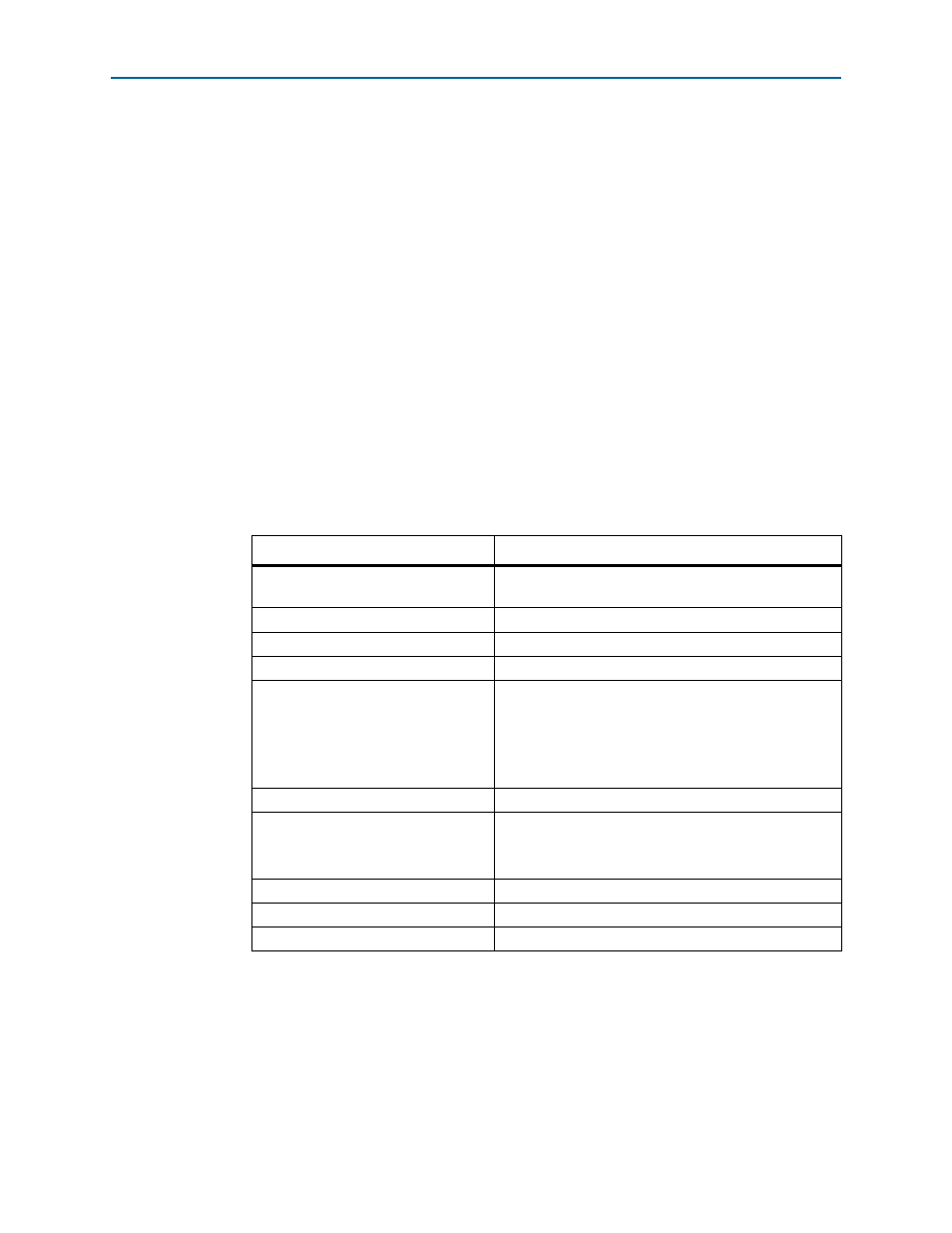

Table C–3. Parameter Values for Autorate Negotiation Testbench Initial Variation

Parameter

Value

Device family

Stratix IV GX, Cyclone IV GX, Arria V, Cyclone V, or

Stratix V

Language

VHDL

File name

(1)

<working directory>\cpri_top_level

Operation mode

Master

(2)

Line rate

Stratix IV GX and Cyclone IV GX variations: 1.2288 Gbps

Arria V GT variations for 9.8 Gbps autorate negotiation:

6.144 Gbps

All other Arria V, Cyclone V, and Stratix V variations:

0.6144 Gbps

Enable auto-rate negotiation

On

Transceiver reference clock frequency

(Arria V, Cyclone V, and Stratix V

variations only)

Arria V GT variations for 9.8 Gbps autorate negotiation:

122.88 MHz

All other 28-nm variations: 61.44 MHz

Include MAC block

On

Include HDLC block

Off

Number of antenna-carrier interfaces

0

Notes to

Table C–3

:

(1) If you use a different path or file name, you must edit the simulation script to refer to the correct file for the DUT.

(2) Altera does not support an example testbench for an RE slave DUT.