Altera CPRI IP Core User Manual

Page 54

4–22

Chapter 4: Functional Description

MAP Interface

CPRI MegaCore Function

December 2013

Altera Corporation

User Guide

1

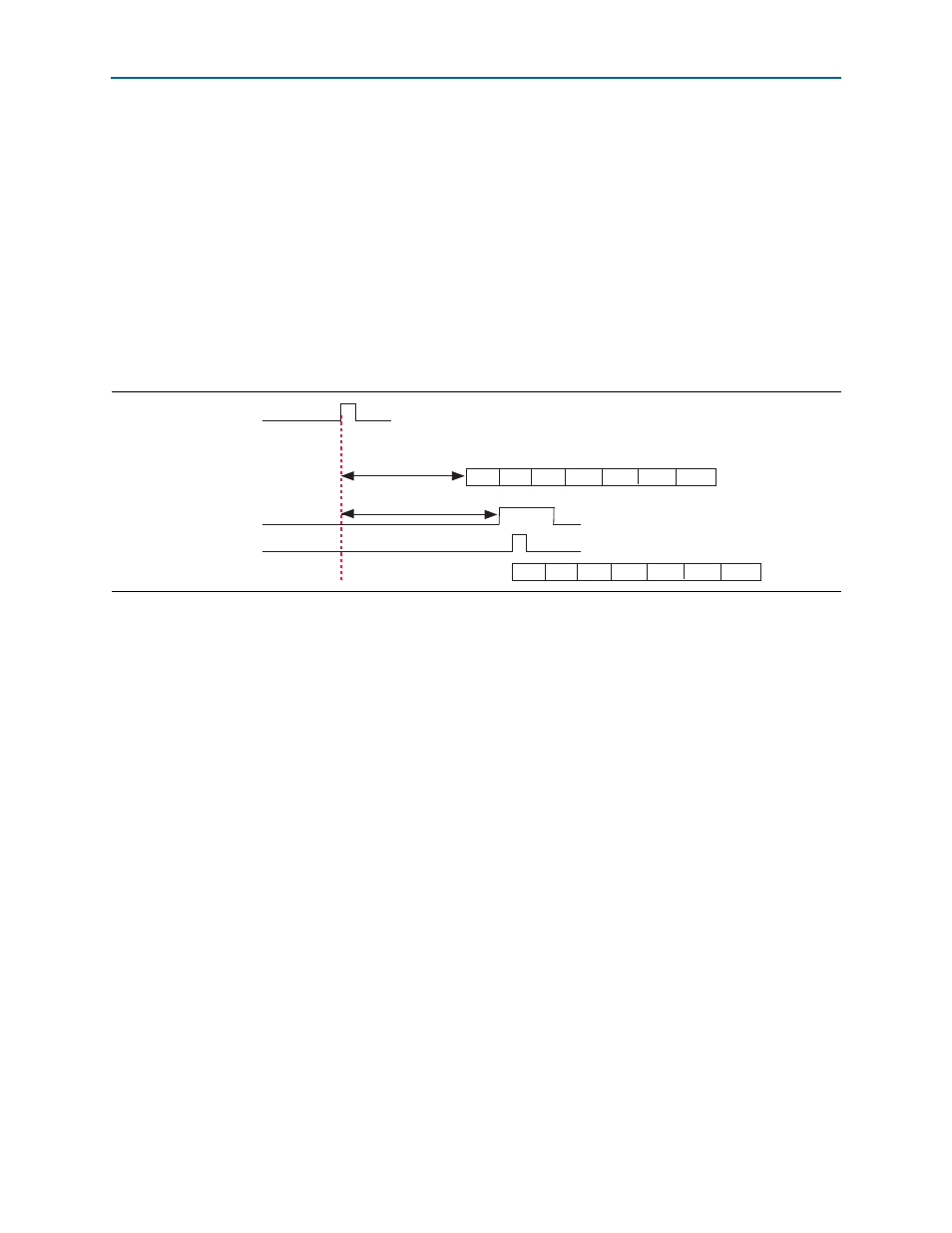

To ensure IP core control over the resynchronization signal timing, Altera

recommends that your application trigger the

mapN_rx_resync

signal with the CPRI

IP core output signal

cpri_rx_start

. The CPRI AUX interface asserts the

cpri_rx_start

signal according to the offset value specified in the

user-programmable

CPRI_START_OFFSET_RX

register.

Asserting the resynchronization signal ensures correct alignment between the RF

implementation and the CPRI basic frame at the appropriate offset from the start of

the 10 ms radio frame. You control the

mapN_rx_resync

signals to ensure that the IP

core accommodates your application-specific constraints.

shows the roles of the

CPRI_START_OFFSET_RX

and

CPRI_MAP_OFFSET_RX

registers in ensuring correct alignment.

The values programmed in the

CPRI_START_OFFSET_RX

register control the assertion of

the

cpri_rx_start

signal. The values in the

start_rx_offset_z

,

start_rx_offset_x

,

and

start_rx_offset_seq

fields specify a hyperframe number, basic frame number,

and word number in the basic frame, respectively, within the 10 ms frame.

The CPRI master transmitter loads the AxC container block on the CPRI link at a

specific location in the 10 ms frame; the system programs the information for this

location in the

CPRI_START_OFFSET_RX

register. The CPRI slave receiver learns the

location of the AxC container block from the

CPRI_START_OFFSET_RX

register.

For example, if the

CPRI_START_OFFSET_RX

register is programmed with the value

0x00020001, the CPRI receiver asserts the

cpri_rx_start

signal at word index 2 of

basic frame 1 of hyperframe 0 in the 10ms frame. The data channel application

samples the

cpri_rx_start

signal, detects it is asserted, and then synchronizes the

received IQ sample to the RX MAP AxC interface by asserting the

mapN_rx_resync

signal. Assertion of the

mapN_rx_resync

signal resets the read pointer of current

antenna-carrier interface (mapN) Rx buffer to zero. The

mapN_rx_data

can safely be

sampled by the data channel one cycle after the

mapN_rx_resync

signal is asserted.

The offset programmed in the

CPRI_MAP_OFFSET_RX

register tells the MAP receiver

interface when to reset the write pointer of the Rx buffer: when the internal counters

match the value in the

CPRI_MAP_OFFSET_RX

register, the write pointer resets. If the

offset in this register has the value of zero, the write pointer resets at the start of every

10 ms radio frame. After the MAP receiver block resets the write pointer, it begins

transferring IQ data from the CPRI frame to the Rx buffer.

Figure 4–11. User-Controlled Delays to the AxC Data Channels in Rx Synchronous Buffer Mode

cpri_rx_start

cpri_rx_rfp / _hfp

mapN_rx_resync

CPRI_START_OFFSET_RX

CPRI_MAP_OFFSET_RX

sample 0 sample 1sample 2 sample 3 sample 4 sample 5 sample 6

sample 0 sample 1sample 2 sample 3 sample 4 sample 5 sample 6

Read from mapN Rx buffer in the first read cycle after the resync signal:

Write to mapN Rx buffer according to CPRI_MAP_OFFSET_RX value: