Map transmitter signals, Map transmitter signals –3, Er to – Altera CPRI IP Core User Manual

Page 101

Chapter 6: Signals

6–3

MAP Interface Signals

December 2013

Altera Corporation

CPRI MegaCore Function

User Guide

MAP Transmitter Signals

The behavior of many of the MAP transmitter interface signals depends on the CPRI

IP core’s current TX synchronization mode. The mode is determined by your selection

in the CPRI parameter editor and by the

CPRI_MAP_CONFIG

register (

), as shown in

.

“MAP Transmitter Interface” on page 4–24

includes a description of signal

handshaking in all three synchronization modes, and timing diagrams that illustrate

the expected behavior of these signals. For a summary of signal availability in the

different synchronization modes, refer to

map{23…0}_rx_resync

Input

Resynchronization signal for use in synchronous buffer mode. When

this signal is asserted, the read pointer of the mapN Rx buffer is reset

to zero. This signal is synchronous to the

mapN_rx_clk

clock.

To ensure valid data in synchronous buffer mode, the application

should only assert the

mapN_rx_resync

signal after the CPRI IP core

asserts the

cpri_rx_start

signal. However, the CPRI IP core does

not enforce this requirement.

In FIFO mode the

map{23...0}_rx_resync

signals do not participate

in data transfer synchronization, and the CPRI IP core ignores these

signals. In the internally-clocked mode, these signals are not present.

map{23…0}_rx_start

Output

In the internally-clocked mode, the CPRI IP core asserts each

mapN_rx_start

signal to indicate the start of valid data on the

corresponding antenna-carrier interface (

mapN_rx_data

) in the

current 10 ms radio frame. This signal is synchronous with the

cpri_clkout

clock. When it asserts

mapN_rx_start

, the CPRI IP

core also asserts the

mapN_rx_valid

signal and transmits valid data

on the corresponding antenna-carrier interface.

In FIFO mode and in synchronous buffer mode, the

map{23...0}_rx_start

signals do not participate in data transfer

synchronization, and the application should ignore these signals.

map{23…0}_rx_status_data[2:0]

Output

This vector contains the following status bits:

[2]

cpri_map_rx_overflow

: Rx FIFO overflow indicator for this

antenna-carrier interface. This signal is synchronous to the

cpri_clkout

clock, and is asserted following a write to a full

buffer. This signal reflects the value in the appropriate bit of the

buffer_rx_overflow

field of the

CPRI_IQ_RX_BUF_STATUS

register (

[1]

cpri_map_rx_underflow

: Rx FIFO underflow indicator for

this antenna-carrier interface. This signal is synchronous to the

cpri_clkout

clock, and is asserted following a read from an

empty buffer. This signal reflects the value in the appropriate bit

of the

buffer_rx_underflow

field of the

CPRI_IQ_RX_BUF_STATUS

register (

).

[0]

cpri_map_rx_en

: Indicates that this antenna-carrier interface

is enabled. The value is determined in the

CPRI_IQ_RX_BUF_CONTROL

register. Use this signal to disable

external logic for inactive AxC interfaces and to map interface

clock gating to save power.

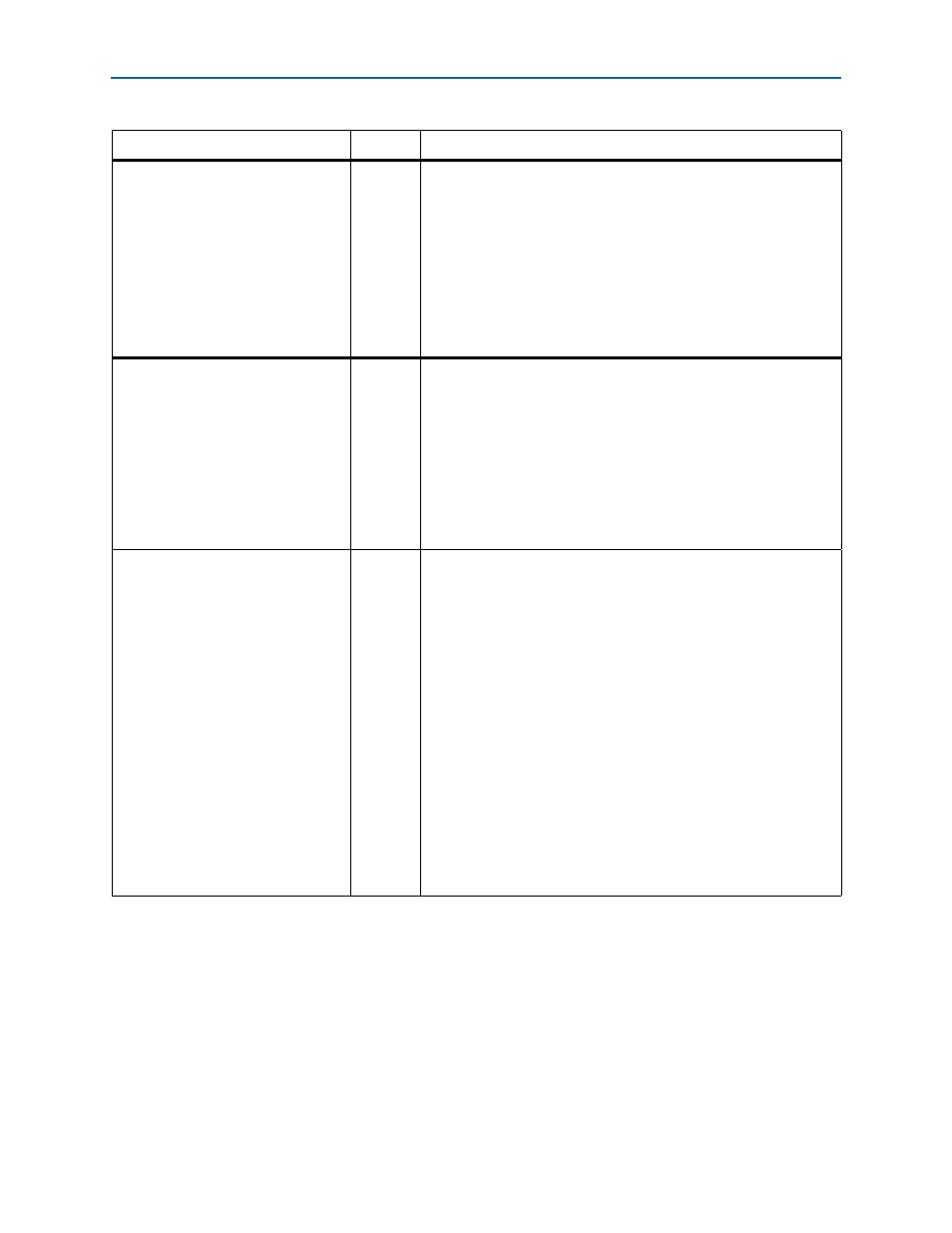

Table 6–1. MAP Receiver Interface Signals (Part 3 of 3)

Signal

Direction

Description