Altera CPRI IP Core User Manual

Page 145

Chapter 7: Software Interface

7–29

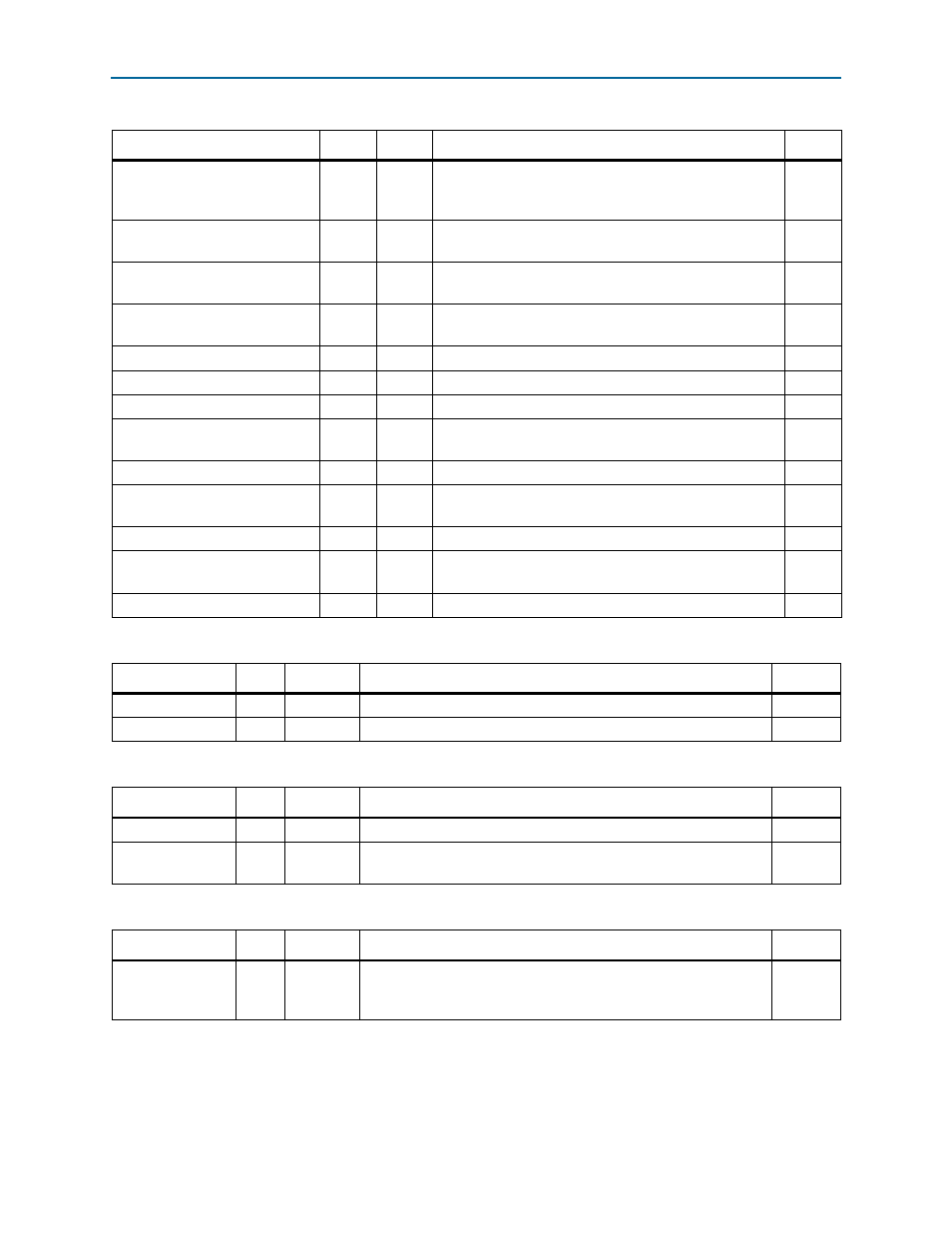

HDLC Registers

December 2013

Altera Corporation

CPRI MegaCore Function

User Guide

intr_rx_ready_block_en

[16]

RW

Indicates an interrupt is generated when

rx_ready_block

is asserted, if

intr_en

and

intr_rx_en

are asserted.

1’h0

intr_rx_ready_end_en

[15]

RW

Indicates an interrupt is generated when

rx_ready_end

is

asserted, if

intr_en

and

intr_rx_en

are asserted.

1’h0

intr_rx_abort_en

[14]

RW

Indicates an interrupt is generated when

rx_abort

is

asserted, if

intr_en

and

intr_rx_en

are asserted.

1’h0

intr_rx_ready_en

[13]

RW

Indicates an interrupt is generated when

rx_ready

is

asserted, if

intr_en

and

intr_rx_en

are asserted.

1’h0

intr_tx_en

[12]

RW

HDLC Tx interrupt enable.

1’h0

intr_rx_en

[11]

RW

HDLC Rx interrupt enable.

1’h0

intr_en

[10]

RW

HDLC global interrupt enable.

1’h0

rx_long_frame_en

[9]

RW

Enable reception of Rx HDLC frames longer than 1536

bytes.

1’h0

RSRV

[8:5]

UR0

Reserved.

4’h0

length_check

[4]

RW

Indicates that a length check is performed on Rx packets,

and those with length less than 64 bytes are discarded.

1’h0

RSRV

[3:2]

UR0

Reserved.

2’h0

little_endian

[1]

RW

Indicates that the HDLC channel receive and transmit data

is formatted in little endian byte order.

1’h0

RSRV

[0]

UR0

Reserved.

1'h0

Table 7–70. HDLC_CONFIG—HDLC Feature Configuration 1—Offset: 0x308 (Part 2 of 2)

Field

Bits

Access

Function

Default

Table 7–71. HDLC_CONFIG_2—HDLC Feature Configuration 2—Offset: 0x30C

Field

Bits

Access

Function

Default

RSRV

[31:1] UR0

Reserved.

31'h0

crc_enable

[0]

RW

Enables insertion of HDLC CRC at the end of the HDLC frame.

1'h0

Table 7–72. HDLC_RX_CONTROL—HDLC Rx Control—Offset: 0x310

Field

Bits

Access

Function

Default

RSRV

[31:1] RO

Reserved.

31'h0

rx_discard

[0]

WO

Indicates that the HDLC receiver module should discard the current

HDLC Rx frame.

1'h0

Table 7–73. HDLC_RX_DATA—HDLC Rx Data—Offset: 0x314

Field

Bits

Access

Function

Default

rx_data

[31:0] RO

HDLC Rx frame data. If the HDLC receiver module takes HDLC data

from this register, if data is not ready when the module expects it, the

HDLC receiver module aborts the packet.

1'h0