Refer to, Table 7–31 on, As shown in – Altera CPRI IP Core User Manual

Page 131

Chapter 7: Software Interface

7–15

MAP Interface and AUX Interface Configuration Registers

December 2013

Altera Corporation

CPRI MegaCore Function

User Guide

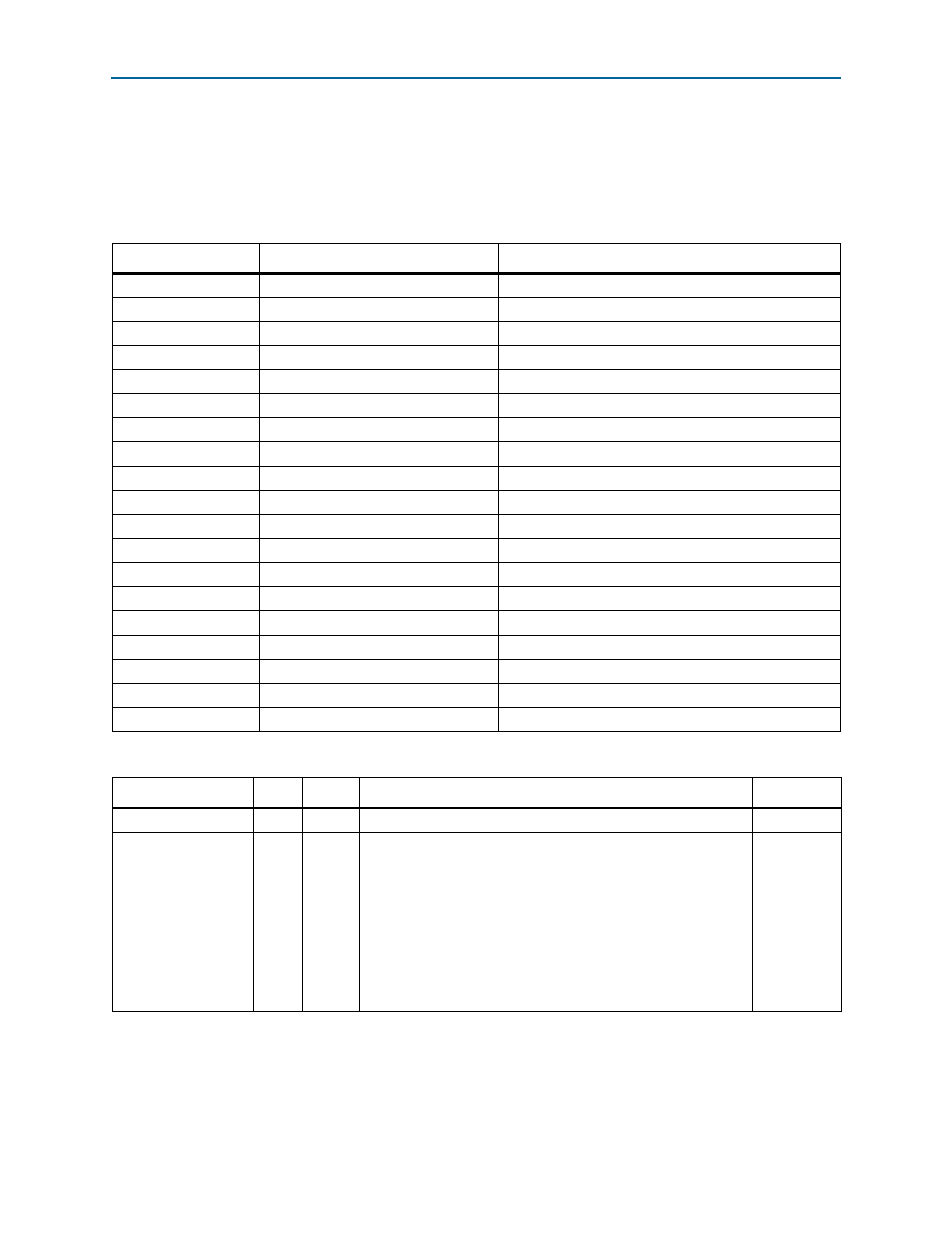

MAP Interface and AUX Interface Configuration Registers

This section lists the MAP interface configuration registers.

provides a

memory map for the MAP interface configuration registers.

through

describe the MAP interface configuration registers in the CPRI IP core.

Table 7–30. MAP Interface Configuration Registers Memory Map

Address

Name

Expanded Name

0x100

CPRI_MAP_CONFIG

CPRI Mapping Features Configuration

0x104

CPRI_MAP_CNT_CONFIG

Basic UMTS/LTE Mapping Configuration

0x108

CPRI_MAP_TBL_CONFIG

K Parameter Config for Advanced Table-Based Mapping

0x10C

CPRI_MAP_TBL_INDEX

Advanced Mapping Configuration Table Index

0x110

CPRI_MAP_TBL_RX

Advanced Mapping Rx Configuration Table

0x114

CPRI_MAP_TBL_TX

Advanced Mapping Tx Configuration Table

0x118

CPRI_MAP_OFFSET_RX

MAP Rx Frame Offset

0x11C

CPRI_MAP_OFFSET_TX

MAP Tx Frame Offset

0x120

CPRI_START_OFFSET_RX

Rx Start Frame Offset

0x124

CPRI_START_OFFSET_TX

Tx Start Frame Offset

0x128

CPRI_MAP_RX_READY_THR

CPRI Mapping Rx Ready Threshold

0x12C

CPRI_MAP_TX_READY_THR

CPRI Mapping Tx Ready Threshold

0x130

CPRI_MAP_TX_START_THR

CPRI Mapping Tx Start Threshold

0x13C

CPRI_PRBS_CONFIG

PRBS Generation Pattern Configuration

0x140–0x144

CPRI_PRBS_STATUS

PRBS Data Validation Status

0x150

CPRI_IQ_RX_BUF_CONTROL

MAP Receiver FIFO Buffer Control

0x160

CPRI_IQ_TX_BUF_CONTROL

MAP Transmitter FIFO Buffer Control

0x180–0x184

CPRI_IQ_RX_BUF_STATUS

MAP Receiver FIFO Buffer Status

0x1A0–0x1A4

CPRI_IQ_TX_BUF_STATUS

MAP Transmitter FIFO Buffer Status

Table 7–31. CPRI_MAP_CONFIG—CPRI Mapping Features Configuration—Offset: 0x100 (Part 1 of 2)

Field

Bits

Access

Function

Default

RSRV

[31:6] UR0

Reserved.

27’h0

map_tx_start_mode

[5]

RW

Selection mode for start-up synchronization on the Tx side. This

field is relevant only when the IP core is in FIFO mode (the Enable

MAP interface synchronization with core clock parameter is

turned off and the

map_tx_sync_mode

field has the value of 0).

Values are:

0: The IP core aligns the first IQ sample it sends on the CPRI

link with the existing start threshold.

1: The IP core aligns the first IQ sample it sends on the CPRI

link with the CPRI frame offset.

1’h0