Table 7–27 – Altera CPRI IP Core User Manual

Page 129

Chapter 7: Software Interface

7–13

CPRI Protocol Interface Registers

December 2013

Altera Corporation

CPRI MegaCore Function

User Guide

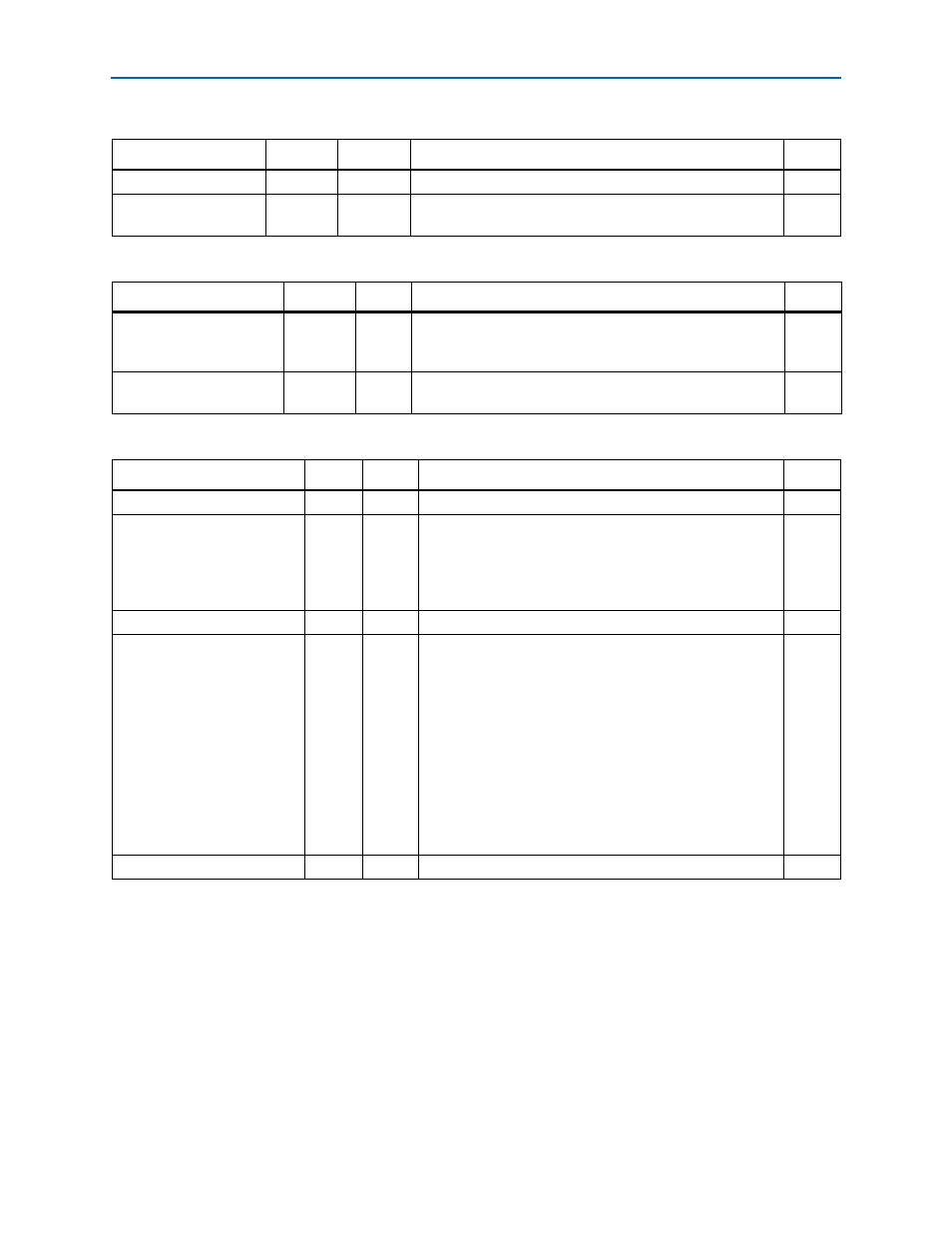

Table 7–26. CPRI_TX_SCR_SEED— Tx Scrambler Seed —Offset: 0x5C

Field Bits

Access

Function

Default

RSRV

[31] UR0

Reserved.

1’h0

tx_scr_seed

[30:0] RW

Transmitter scrambler seed. If the seed has value 0, the

transmission is not scrambled.

31’h0

Table 7–27. CPRI_RX_SCR_SEED— Rx Scrambler Support —Offset: 0x60

Field

Bits

Access Function Default

rx_scr_act_indication

[31] RO

Indicates that the incoming hyperframe is scrambled. The

value 1 indicates that the incoming communication is

scrambled, and the value 0 indicates that it is not scrambled.

1’h0

rx_scr_seed

[30:0] RO

Received scrambler seed. The receiver descrambles the

incoming CPRI communication based on this seed.

31’h0

Table 7–28. CPRI_TX_BITSLIP— Tx Bitslip —Offset: 0x64

Field Bits

Access

Function

Default

RSRV

[31:21] UR0

Reserved.

11’h0

rx_

bitslipboundaryselectout

[20:16] RO

Number of bits of delay (bitslip) detected at the receiver

word-aligner. Value can change at frame synchronization,

when the transceiver is resetting. Any K28.5 symbol position

change that occurs when word alignment is activated

changes the bitslip value.

5’h0

RSRV

[15:9] UR0

Reserved.

7’h0

tx_bitslip_en

[8] RW

Enable manual

tx_bitslipboundaryselect

updates.

When this bit has the value of 0 in a CPRI RE slave, the CPRI

RE slave determines the value in the

tx_bitslipboundaryselect

field, and adds

tx_bitslipboundaryselect

bits of delay in the

transceiver transmitter to compensate for the variability in

the Rx word aligner bitslip. The CPRI IP core ignores the

value in the

tx_bitslipboundaryselect

field in a CPRI

REC or RE master. When the

tx_bitslip_en

bit has the

value of 1, the application can write a value to the

tx_bitslipboundaryselect

field to manually override the

value the CPRI IP core would calculate.

1’h0

RSRV

[7:5] UR0

Reserved.

3’h0