Table 7–9 on, Table 7–8, Table 7–9 – Altera CPRI IP Core User Manual

Page 122: Table 7–12, Table 7–12 on

7–6

Chapter 7: Software Interface

CPRI Protocol Interface Registers

CPRI MegaCore Function

December 2013

Altera Corporation

User Guide

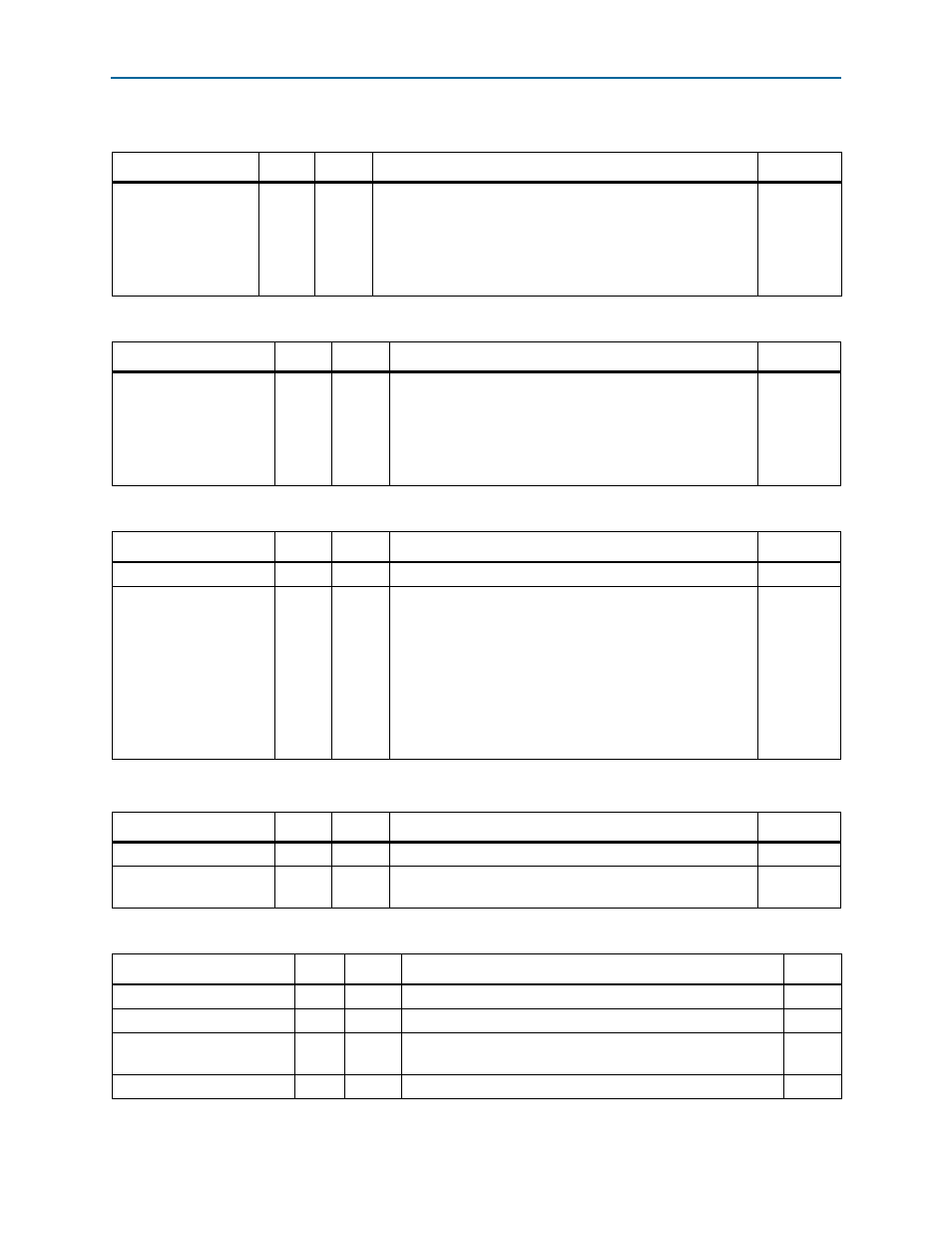

Table 7–8. CPRI_RX_CTRL—CPRI Received Control Word—Offset: 0x10

Field

Bits

Access

Function

Default

rx_control_data

[31:0]

RW

Most recent received CPRI control word 32-bit section from

CPRI hyperframe position Z.x, where x is the index in the

cpri_ctrl_index

field of the

CPRI_CTRL_INDEX

register. The

cpri_ctrl_position

field of the

CPRI_CTRL_INDEX

register

indicates whether this is the first, second, third, or fourth such

32-bit section.

32'h0

Table 7–9. CPRI_TX_CTRL—CPRI Transmit Control Word—Offset: 0x14

Field

Bits

Access

Function

Default

tx_control_data

[31:0]

RW

CPRI control word 32-bit section to be transmitted in CPRI

hyperframe position Z.x, where x is the index in the

cpri_ctrl_index

field of the

CPRI_CTRL_INDEX

register.

The

cpri_ctrl_position

field of the

CPRI_CTRL_INDEX

register indicates whether this is the first, second, third, or

fourth such 32-bit section.

32'h0

Table 7–10. CPRI_LCV—CPRI Line Code Violation Counter—Offset: 0x18

Field

Bits

Access

Function

Default

RSRV

[31:8]

UR0

Reserved.

24'h0

cpri_lcv

[7:0]

RO

Number of line code violations (LCVs) detected in the 8B/10B

decoding block in the transceiver. Enables CPRI link

debugging. This register saturates at the value 255; after it

reaches 255, it maintains this value until reset.

This counter is not used to determine whether the N_LCV

threshold (

) is reached, because it

includes LCVs that occur during initialization—before T_LCV

(

) is reached—and because it

saturates.

8’h0

Table 7–11. CPRI_BFN—CPRI Recovered Radio Frame Counter—Offset: 0x1C

Field

Bits

Access

Function

Default

RSRV

[31:12] UR0

Reserved.

20'h0

bfn

[11:0]

RO

Current BFN (node B radio frame number) number. Value

obtained from BFN alignment state machine.

12’h0

Table 7–12. CPRI_HW_RESET—Hardware Reset From Control Word—Offset: 0x20 (Part 1 of 2)

Field

Bits

Access

Function

Default

RSRV

[31:8]

UR0

Reserved.

24'h0

reset_gen_done_hold

[7]

RC

Hold

reset_done

.

1’h0

reset_gen_done

[6]

RO

Indicates that a reset request or acknowledgement has been

successfully sent on the CPRI link by the CPRI transmitter.

1'h0

reset_detect_hold

[5]

RC

Hold

reset_detect

.

1'h0