Media independent interface to an external – Altera CPRI IP Core User Manual

Page 69

Chapter 4: Functional Description

4–37

Media Independent Interface to an External Ethernet Block

December 2013

Altera Corporation

CPRI MegaCore Function

User Guide

previous value.

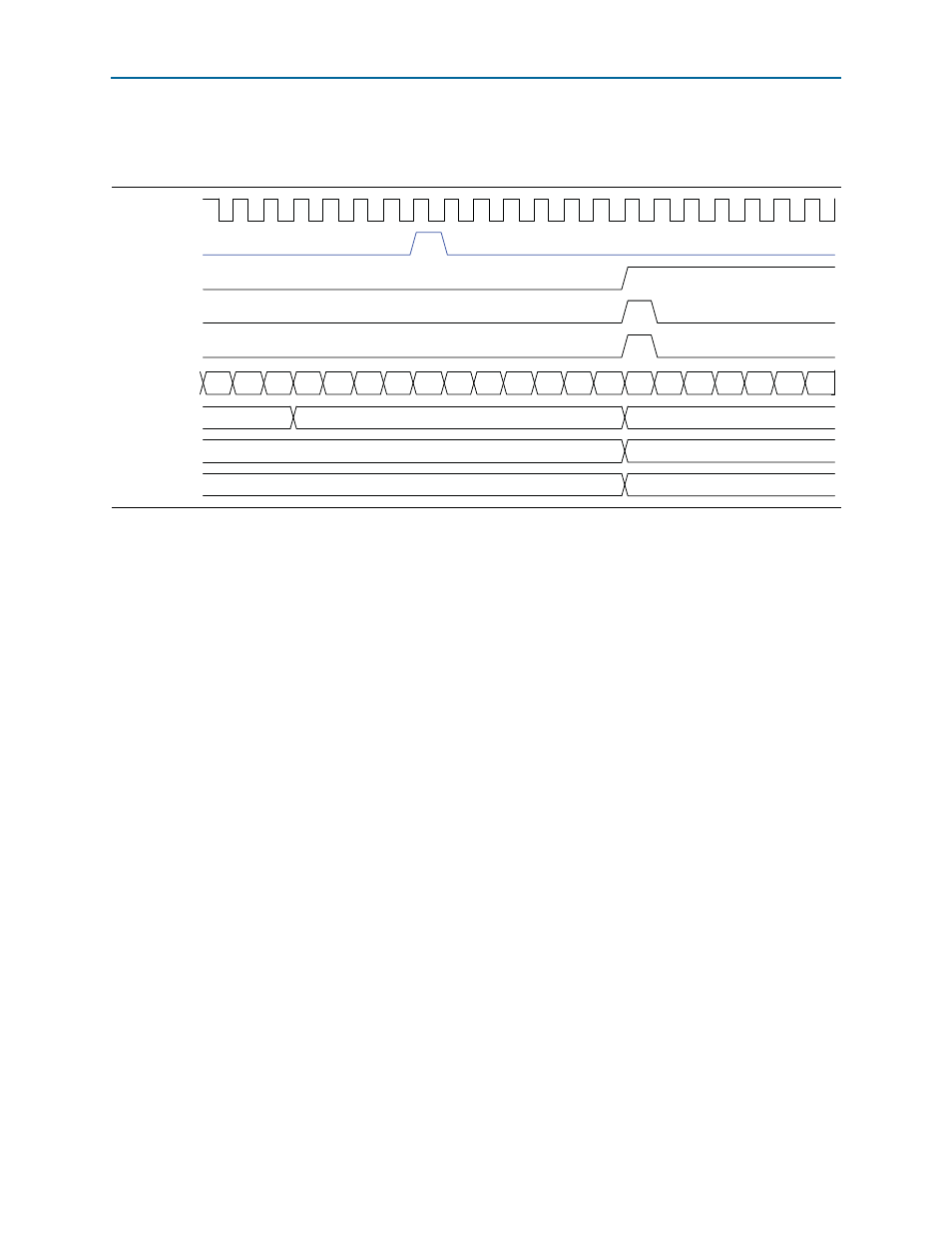

illustrates the behavior of the CPRI IP core signals in

response to the

cpri_tx_sync_rfp

pulse.

For more information about the relationships between the synchronization pulses and

numbers, refer to

. For the mapping of data between the

AUX interface and the CPRI link, refer to

The

cpri_tx_aux_data

and

cpri_tx_aux_mask

signals are fields of the

aux_tx_mask_data

bus. The other signals described in the preceding list are fields of

the

aux_tx_status_data

bus. For additional information about the AUX transmitter

signals, refer to

.

Media Independent Interface to an External Ethernet Block

The media independent (MI) interface, or MII, allows the CPRI IP core to

communicate directly with an external Ethernet MAC block, replacing the internal

Ethernet MAC. You specify in the CPRI parameter editor whether to implement this

interface or to use the Ethernet MAC block available with the CPRI IP core. The two

options are mutually exclusive.

If you configure the CPRI IP core with the MII, you must implement the Ethernet

MAC block outside the CPRI IP core.

The MI interface is not a true media-independent interface, because it is clocked by

the

cpri_clkout

clock (which drives the

cpri_mii_txclk

and

cpri_mii_rxclk

clock

signals directly), whose frequencies do not match the usual 2.5 MHz and 25 MHz

frequencies of the media-independent protocol specification. If you use this interface,

your external Ethernet block must communicate with the CPRI IP core synchronously

with the

cpri_mii_txclk

and

cpri_mii_rxclk

clocks.

The MII supports the bandwidth described in the CPRI V5.0 Specification in Table 12,

Achievable Ethernet bit rates.

Figure 4–21. CPRI REC Master Response to cpri_tx_sync_rfp Resynchronization Pulse

cpri_clkout

cpri_tx_sync_rfp

cpri_tx_seq

cpri_tx_x

cpri_tx_hfn

cpri_tx_bfn

cpri_tx_hfp

cpri_tx_start

cpri_tx_rfp

5

6

7

0

1

2

3

4

5

6

7

8

9

10

0

1

2

3

4

5

6

3

4

0

3

0

2

3