Altera CPRI IP Core User Manual

Page 150

8–2

Chapter 8: CPRI IP Core Demonstration Testbench

CPRI MegaCore Function

December 2013

Altera Corporation

User Guide

To generate a testbench that demonstrates autorate negotiation, you must turn on

Enable auto-rate negotiation

and Include MAC block, but turn off Include HDLC

block

and set Number of antenna-carrier interfaces to the value of zero. For

information about the testbench that supports auto-rate negotiation, refer to

Appendix C, CPRI Autorate Negotiation Testbench

The non-autorate negotiation testbench demonstrates the following functions:

■

Writing to the registers

■

Frame synchronization process

■

Transmission and reception of CPRI link data on the AUX interface and on any

additional data interfaces you configure in the CPRI parameter editor

The testbench initializes the CPRI IP core and sends the generated data to the CPRI IP

core interfaces listed in

. The CPRI IP core’s high-speed transceiver output is

looped back to its high-speed transceiver input. The testbench module provides

clocking, reset, and initialization control, and processes to write to and read from the

IP core’s interfaces. The testbench communicates with the CPRI IP core HDLC block

through the IP core’s CPU interface. The initialization process requires that the

testbench module write to the CPRI IP core registers through its CPU interface.

MII

Supports enabling of IP core insertion of Ethernet HALT symbol by

asserting the

cpri_mii_txer

input signal to the IP core.

HDLC

The HDLC bit rate is 480 Kbps by default. You can change the HDLC

bit rate by programming the

tx_slow_cm_rate

field of the

CPRI_CM_CONFIG

register. To program this register field, you must

edit the generated testbench file to include the register write

operation.

Table 8–1. Testbench Supported Interface Configurations

Interface

Supported Mode

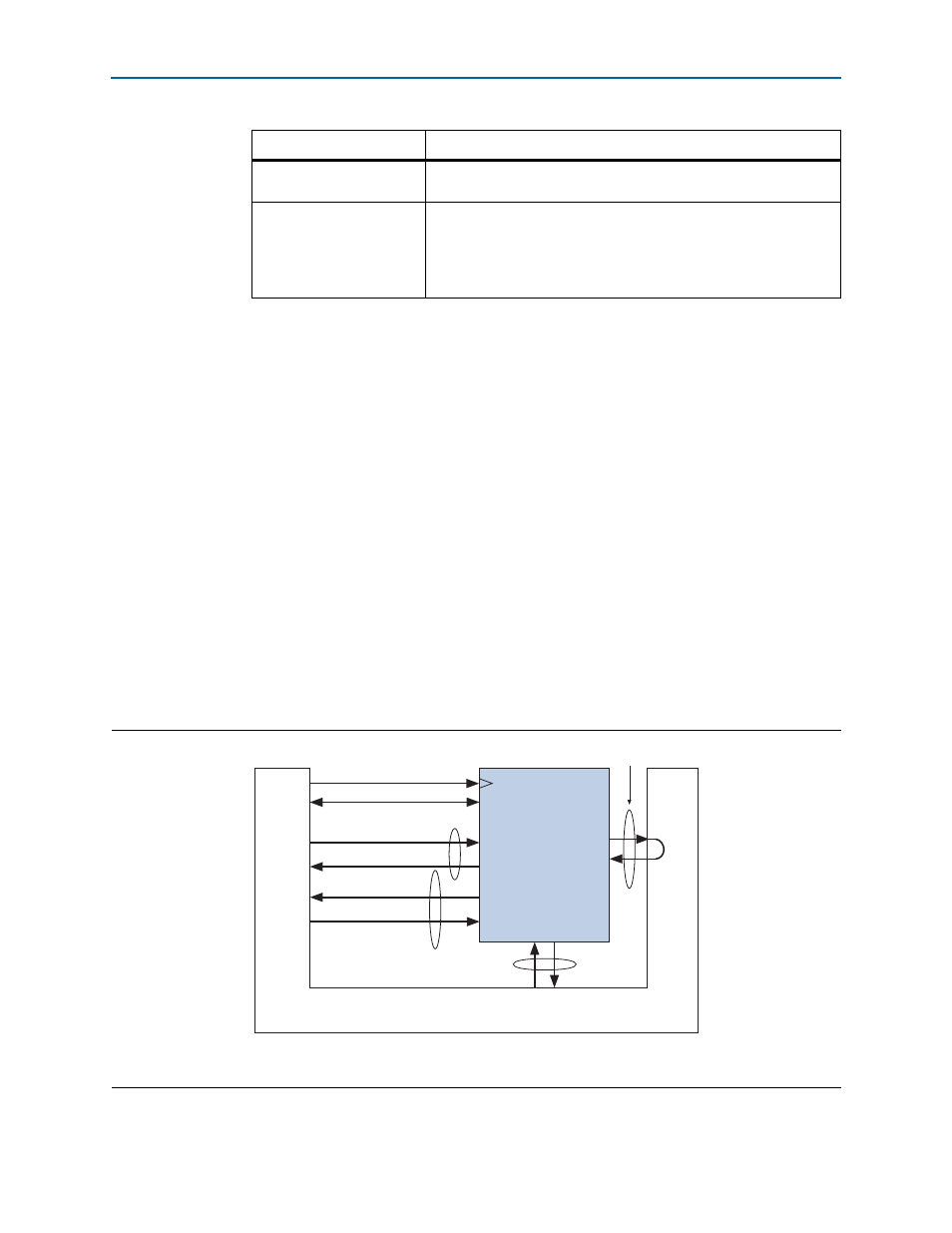

Figure 8–1. CPRI IP Core Demonstration Testbench

Note to

(1) CPU and HDLC transactions occur on the Avalon-MM CPU interface of the CPRI IP core.

rxdatain

txdataout

CPRI

IP Core

MAP_N

CPRI

Link

Avalon-MM

Interface

AUX

Altera

Testbench

gxb_txdataout

Avalon-ST

Rx Interface

Avalon-ST

Tx AUX Interface

aux_tx_status_data,

aux_rx_status_data

aux_tx_mask_data

Avalon-ST

Rx AUX Interface

Avalon-ST

Tx Interface

MII Interface

gxb_rxdatain

CPU Interface

Reference Clock