Extended tx delay, Table e–6 on, Extended tx – Altera CPRI IP Core User Manual

Page 192: Delay measurement, R to, Tx bitslip delay” on, Fixed tx core

E–14

Appendix E: Delay Measurement and Calibration

Single-Hop Delay Measurement

CPRI MegaCore Function

December 2013

Altera Corporation

User Guide

Fixed Tx Core Delay Component

In the Tx path in CPRI IP core variations other than the Arria V GT variations

configured at 9.8 Gbps, the following are fixed delays:

■

Delay from the AUX interface to the Tx elastic buffer (component 1 in

). This delay has a fixed value of four

cpri_clkout

cycles.

■

Delay from the Tx elastic buffer to the Tx transceiver (component 4 in

). This delay depends on the device family and CPRI

data rate.

The sum of these two delays is the fixed delay component of the delay labeled

T_T4 in

Figure E–1 on page E–2

.

shows the sum of these two fixed delays in the different device families.

In CPRI IP core variations with a CPRI line rate of 9.8 Gbps that target an

Arria V GT device, the fixed Tx core delay component extends to the transceiver.

Extended Tx Delay Measurement

The latency of the Tx elastic buffer depends on the number of 32-bit words

currently stored in the buffer, and the phase difference between the system clock

cpri_clkout

, which is used to write data to the buffer, and the transceiver clock

tx_clkout

, which is used to read data from the buffer.

The calculation of the extended Tx delay is identical to the description and

example of extended Rx delay measurement in

, with the substitution of

tx

for

rx

in all the register

field names.

Tx Bitslip Delay

To increase the consistency of the round-trip delay, the CPRI RE slave introduces a

variable bitslip on the Tx path to complement the variability in the word aligner

on the Rx path. The word aligner is encapsulated in the transceiver block. The

word aligner introduces delay variability that is captured in the values described

in

Table E–1 on page E–5

and

Table E–7 on page E–16

and their associated notes.

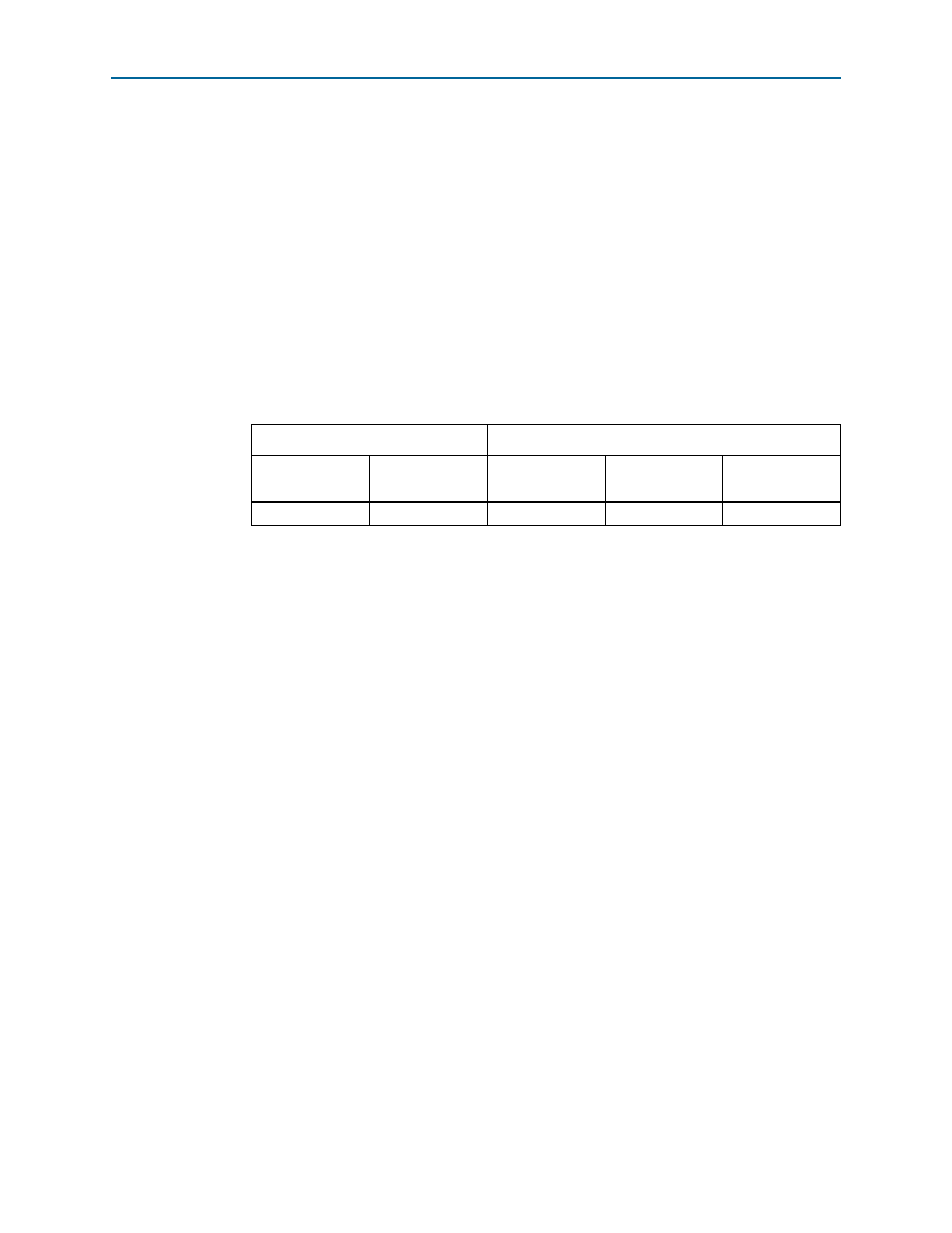

Table E–6. Fixed Latency T_T4 in cpri_clkout Cycles

Data Rate 614.4 Mbps

Data Rate > 614.4 Mbps

Arria II GX

Device

All Other Device

Families

Arria II GX

Device

Cyclone IV GX

Device

All Other Device

Families

5 or 5.25

4.75

6 or 6.5

5.5

7

Note to

:

(1) The first number applies for CPRI IP core variations in which you do not enable autorate negotiation in the CPRI

parameter editor (prior to IP core generation), and the second number applies for CPRI IP core variations in which

you enable autorate negotiation in the CPRI parameter editor.