Cpri ip core demonstration testbench, Chapter 8. cpri ip core demonstration testbench, Chapter 8, cpri ip core demonstration testbench – Altera CPRI IP Core User Manual

Page 149

December 2013

Altera Corporation

CPRI MegaCore Function

User Guide

8. CPRI IP Core Demonstration Testbench

The Altera CPRI IP core includes a demonstration testbench. Depending on your

CPRI IP core variation, the testbench exercises the data interfaces of the IP core or

demonstrates autorate negotiation. In some cases your CPRI IP core may include both

types of testbench.

This chapter describes the testbench that exercises the data interfaces of the IP core.

For information about the testbench that demonstrates autorate negotiation, refer to

Appendix C, CPRI Autorate Negotiation Testbench

The non-autorate negotiation testbench exercises the interfaces you configure in your

CPRI IP core. It provides an example of how to use the Avalon-MM and Avalon-ST

interfaces to generate and process CPRI transactions using the MII, MAP, and AUX

interfaces. The testbench demonstrates HDLC communication in CPRI IP cores that

instantiate an HDLC block.

1

The testbench is available only if you turn on Generate Example Design when

prompted during generation of the CPRI IP core. Refer to

.

Testbenches are available only for certain CPRI IP core variations. However, the

Quartus II software provides the identical Generate Example Design prompt in all

cases.

The non-autorate negotiation testbench exercises only certain synchronization and

mapping modes. Therefore, certain CPRI IP core instances do not simulate

successfully with the generated testbench. To ensure your CPRI variation has a

testbench you can simulate, set the following values in the CPRI parameter editor:

■

Operation mode

must have the value of Master.

■

If the IP core variation has a MAP interface, Mapping mode must have the value

of All or Basic.

■

If the IP core variation has a MAP interface, Enable MAP interface

synchronization with core clock

must be turned off.

lists the interface configurations the testbench exercises.

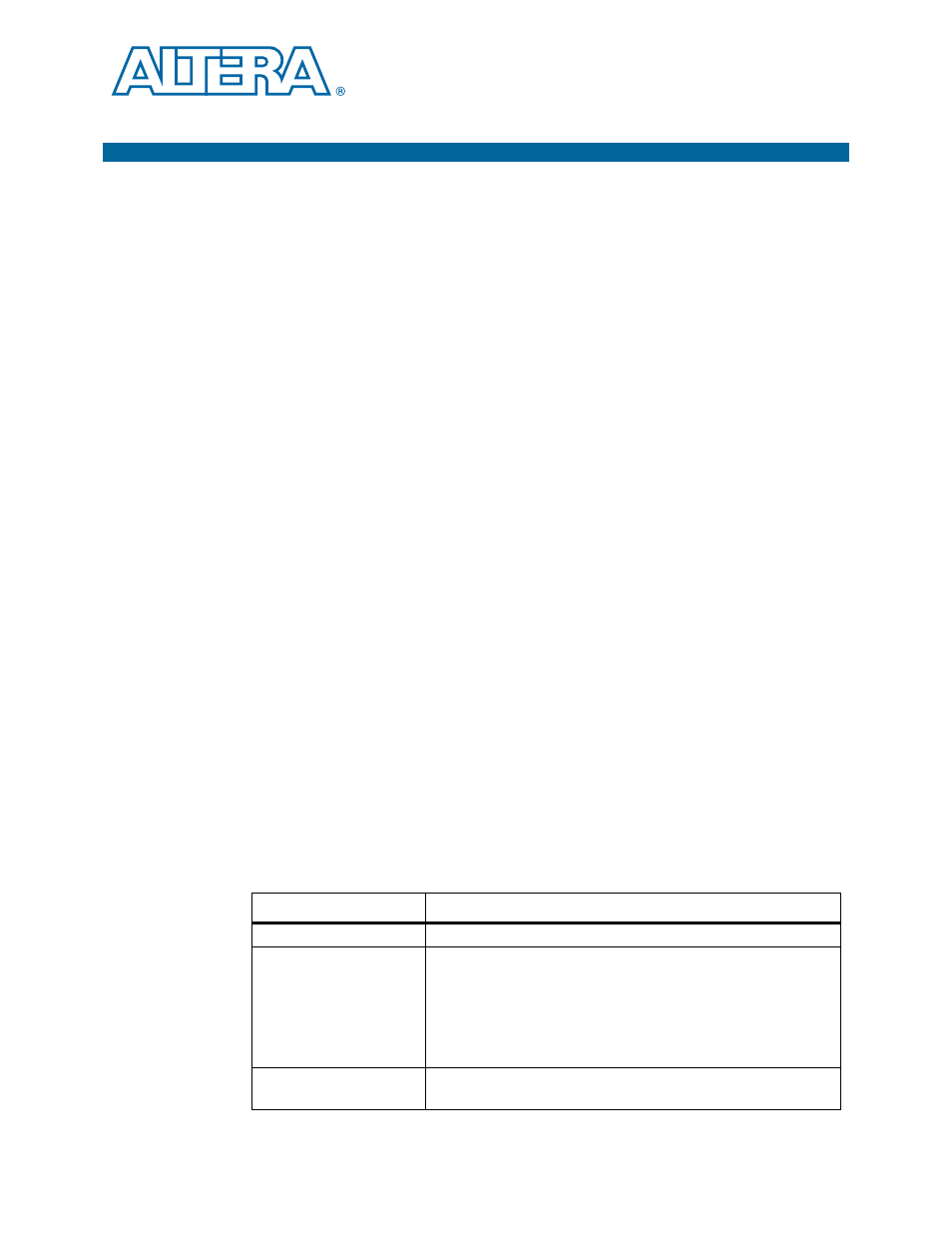

Table 8–1. Testbench Supported Interface Configurations

Interface

Supported Mode

CPU

Single-cycle read and write transactions.

MAP

Basic, FIFO mode only.

SYNC_MAP == 0 (a prerequisite for FIFO mode).

Sampling rate of 3.84 Mbps.

16-bit mode on MAP interface.

Twenty-four or fewer channels.

AUX

Supports AUX data masking (to allow simultaneous communication

on the AUX, CPU, MAP and MI interfaces).