Cpri mii signals, Cpri mii receiver signals, Cpri mii transmitter signals – Altera CPRI IP Core User Manual

Page 108: Cpri mii signals –10, Cpri mii, R to, Cpri mii receiver

6–10

Chapter 6: Signals

CPRI MII Signals

CPRI MegaCore Function

December 2013

Altera Corporation

User Guide

CPRI MII Signals

Table 6–6

and

Table 6–7

list the signals used by the CPRI MII module of the CPRI IP

core. The CPRI MII is enabled if you turn off Include MAC block in the CPRI

parameter editor. The CPRI MII signals are available only if you enable the CPRI MII.

For information about the MII handshaking protocol implementation, refer to

Independent Interface to an External Ethernet Block” on page 4–37

.

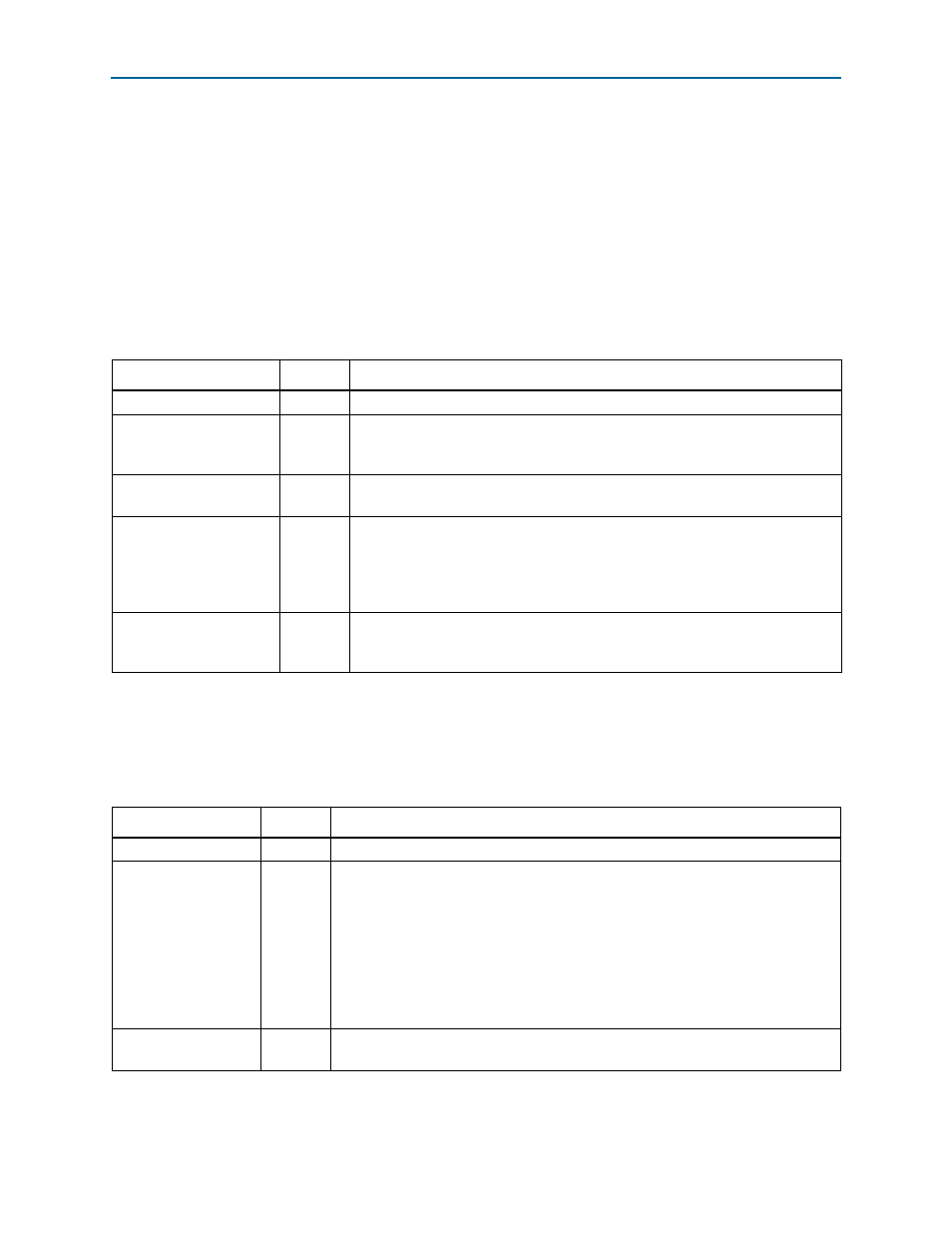

CPRI MII Receiver Signals

Table 6–6

lists the CPRI MII receiver signals.

CPRI MII Transmitter Signals

Table 6–7

lists the CPRI MII transmitter signals. These signals are available if you

exclude the MAC block from the CPRI IP core.

Table 6–6. CPRI MII Receiver Interface Signals

Signal

Direction

Description

cpri_mii_rxclk

Output

Clocks the MII receiver interface. The

cpri_clkout

clock drives this signal.

cpri_mii_rxwr

Output

Ethernet write signal. Indicates the presence of a new K nibble or data value on

cpri_mii_rxd[3:0]

. This signal is asserted during the first

cpri_mii_rxclk

cycle in which the K nibble or a new data value appears on

cpri_mii_rxd[3:0]

.

cpri_mii_rxdv

Output

Ethernet receive data valid. Indicates the presence of valid data or initial K nibble on

cpri_mii_rxd[3:0]

.

cpri_mii_rxer

Output

Ethernet receive error. Indicates an error in the current nibble of

cpri_mii_rxd

or

indicates that the CPRI link is not initialized, and therefore an error might be

present in the frame being transferred to the external Ethernet block. This signal is

deasserted at reset, and asserted after reset until the CPRI IP core achieves frame

synchronization.

cpri_mii_rxd[3:0]

Output

Ethernet receive nibble data. Data bus for data from the CPRI IP core to the

external Ethernet block. All bits are deasserted during reset, and all bits are

asserted after reset until the CPRI IP core achieves frame synchronization.

Table 6–7. CPRI MII Transmitter Interface Signals (Part 1 of 2)

Signal

Direction

Description

cpri_mii_txclk

Output

Clocks the MII transmitter interface. The

cpri_clkout

clock drives this signal.

cpri_mii_txen

Input

Valid signal from the external Ethernet block, indicating the presence of valid data on

cpri_mii_txd[3:0]

. This signal is also asserted while the CPRI MII transmitter

block inserts J and K nibbles in the data stream to form the start-of-packet symbol.

This signal is typically asserted one cycle after

cpri_mii_txrd

is asserted. After that

first cycle following the assertion of cpri_mii_txrd, if cpri_mii_txen is not yet asserted,

the CPRI MII transmitter module inserts Idle cycles until the first cycle in which

cpri_mii_txen

is asserted. If

cpri_mii_txen

is asserted and subsequently

deasserted while

cpri_mii_txrd

remains asserted, the CPRI MII transmitter module

inserts the end-of-packet sequence.

cpri_mii_txer

Input

Ethernet transmit coding error. When this signal is asserted, the CPRI IP core inserts

an Ethernet HALT symbol in the data it passes to the CPRI link.