Altera CPRI IP Core User Manual

Page 215

Additional InformationAdditional Information

Info–3

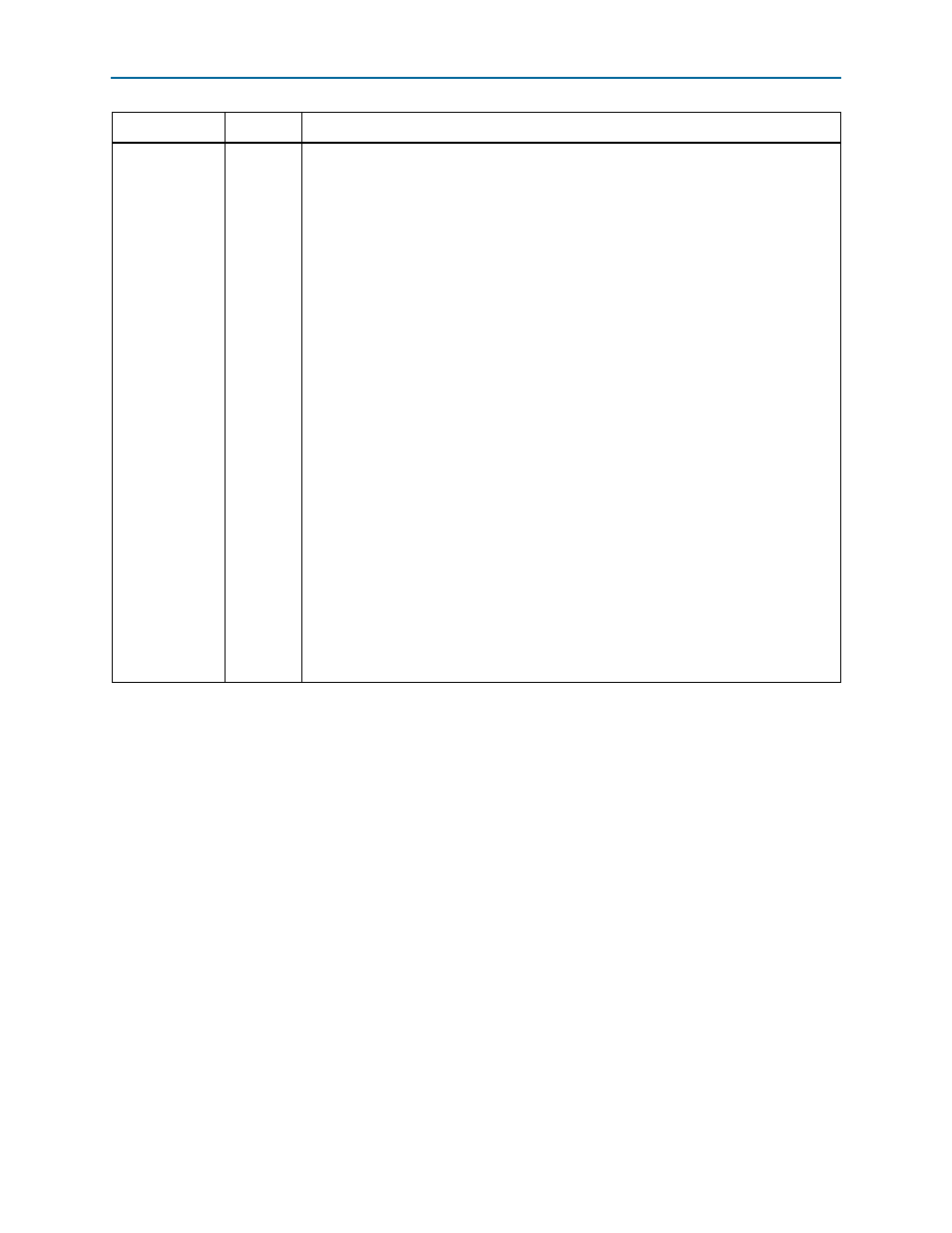

Document Revision History

December 2013

Altera Corporation

CPRI MegaCore Function

User Guide

February 2013,

continued

12.1 SP1,

continued

■

Updated

Appendix B, Implementing CPRI Link Autorate Negotiation

with new

information about configuring the Altera Transceiver Reconfiguration Controller in

Arria V GX and Arria V GT devices.

■

Updated

Figure 8–6 on page 8–5

to reflect new PHY autorate negotiation testbench

handling of Altera Transceiver Reconfiguration Controller.

■

Separated master and slave clocking diagrams for Arria V GT variations with CPRI line

rate 9.8304 Gbps and added detail. New figures are

Figure 4–4 on page 4–8

and

Figure 4–5 on page 4–9

.

■

Updated

Appendix D, Delay Measurement and Calibration

for new release.

■

Moved instructions to create assignments for high-speed transceiver VCCH settings

from

“Specifying Parameters” on page 2–2

to

“Specifying Constraints” on page 2–6

.

■

Moved instructions for instantiating additional transceiver support IP cores from

“Specifying Parameters” on page 2–2

to new section

“Supporting the Transceivers” on

page 2–5

.

■

Placed

“Specifying Constraints”

and

“Supporting the Transceivers”

in new section

“Integrating the CPRI IP Core in a Design” on page 2–5

.

■

Fixed expected

reconfig_clk

frequency in Arria V, Cyclone V, and Stratix V designs, in

Table 6–14 on page 6–15

.

■

Fixed description of

CPRI_EX_DELAY_CONFIG

register (

Table 7–19 on page 7–10

) to

unify

tx_ex_delay

and

rx_ex_delay

fields into single register field

ex_delay

, and

updated all references to the field name.

■

Updated description of

CPRI_EX_DELAY_STATUS

register (

Table 7–20 on page 7–10

) to

unify

tx_ex_buf_delay_valid

and

rx_ex_buf_delay_valid

fields into single

register field

ex_buf_delay_valid

, and updated all references to the field name.

■

Fixed description of

cpu_irq_vector[4:0]

in

Table 6–8 on page 6–11

.

■

Fixed assorted typos.

Date

Version

Changes Made