Sample ladder logic, Appendix objective, Appendix e – Rockwell Automation DAG6.5.8 APPLICATION GUIDE SCADA SYSTEM User Manual

Page 383: Appendix

1

Publication AG-UM008C-EN-P - February 2005

Appendix

E

Sample Ladder Logic

Appendix Objective

This appendix provides guidance for developing your messaging logic

for MicroLogix, SLC 500, PLC-5, and Logix processors.

The user of and those responsible for applying the information

contained in this appendix must satisfy themselves as to the

acceptability of each application and use of the program. In no event

will Rockwell Automation be responsible or liable for indirect or

consequential damages resulting from the use or application of this

information.

The examples shown in this appendix are intended solely to illustrate

the principles of the controllers and some of the methods used to

apply them. Rockwell Automation cannot assume responsibility or

liability for actual use based upon the examples shown.

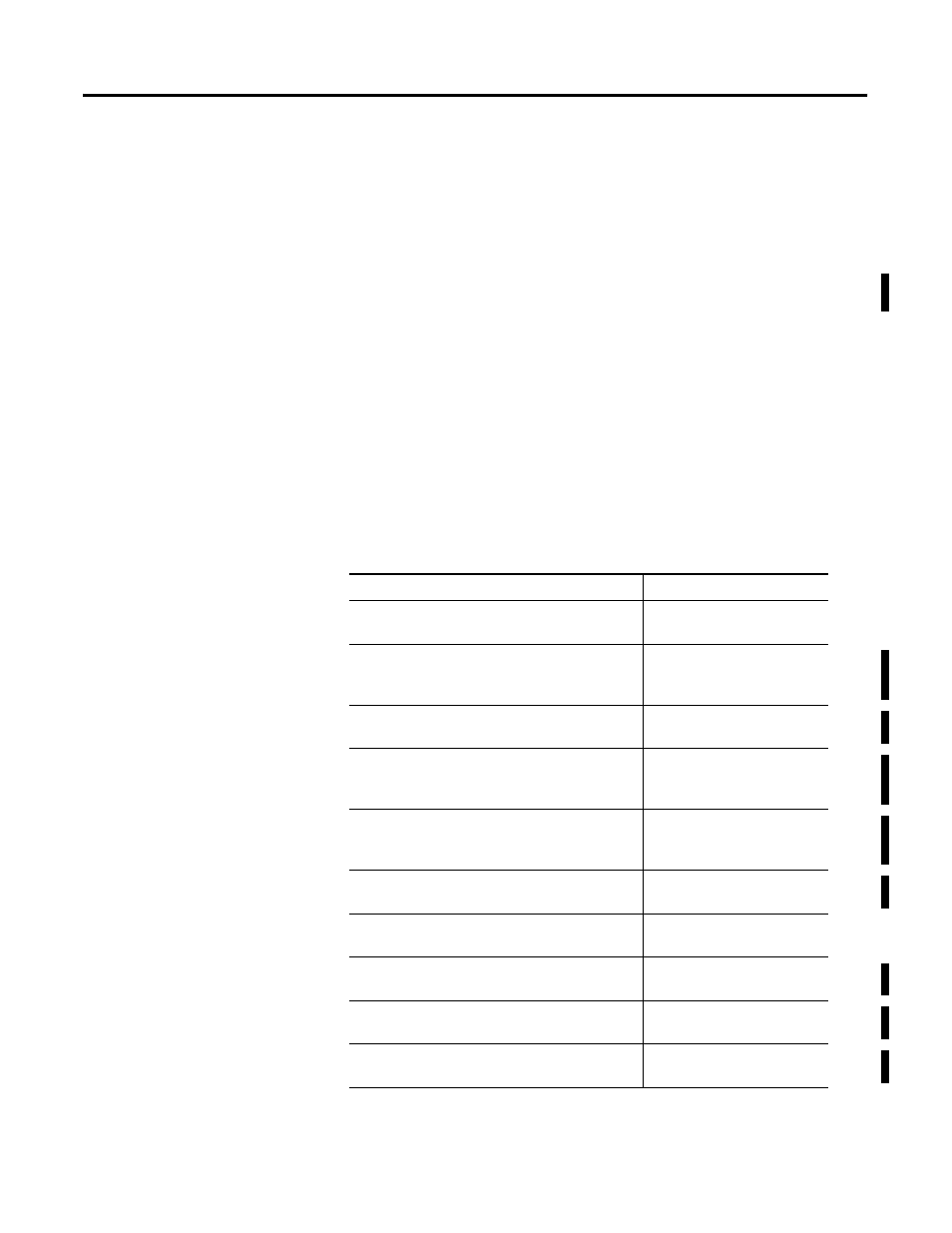

For sample ladder logic on

See page

SLC DF1 Half-Duplex Master

Standard Mode, Master-initiated MSG

SLC DF1 Half-Duplex Master

Message-based Mode and DF1 Radio Modem

initiated MSG

SLC DF1 Half-Duplex Slave and DF1 Radio Modem

Report-By-Exception MSG

PLC-5 and MicroLogix 1100/1200/1500 DF1

Half-Duplex Master Standard Mode,

Master-initiated MSG

PLC-5 and MicroLogix 1100/1200/1500 DF1

Half-Duplex Master Message-based,

Master-initiated MSG

PLC-5 and MicroLogix 1100/1200/1500 DF1

Half-Duplex Slave Report-By-Exception MSG

MicroLogix 1000 Analog DF1 Half-Duplex Slave

Report-by-Exception MSG

Logix DF1 Half-Duplex Master

Standard Mode, Master-initiated MSG

Logix DF1 Half-Duplex Master

Message-based Mode, Master-initiated MSG

Logix DF1 Half-Duplex Slave

Report-By-Exception MSG