Rainbow Electronics W90P710CDG User Manual

Page 99

W90P710CD/W90P710CDG

Publication Release Date: September 19, 2006

- 99 -

Revision B2

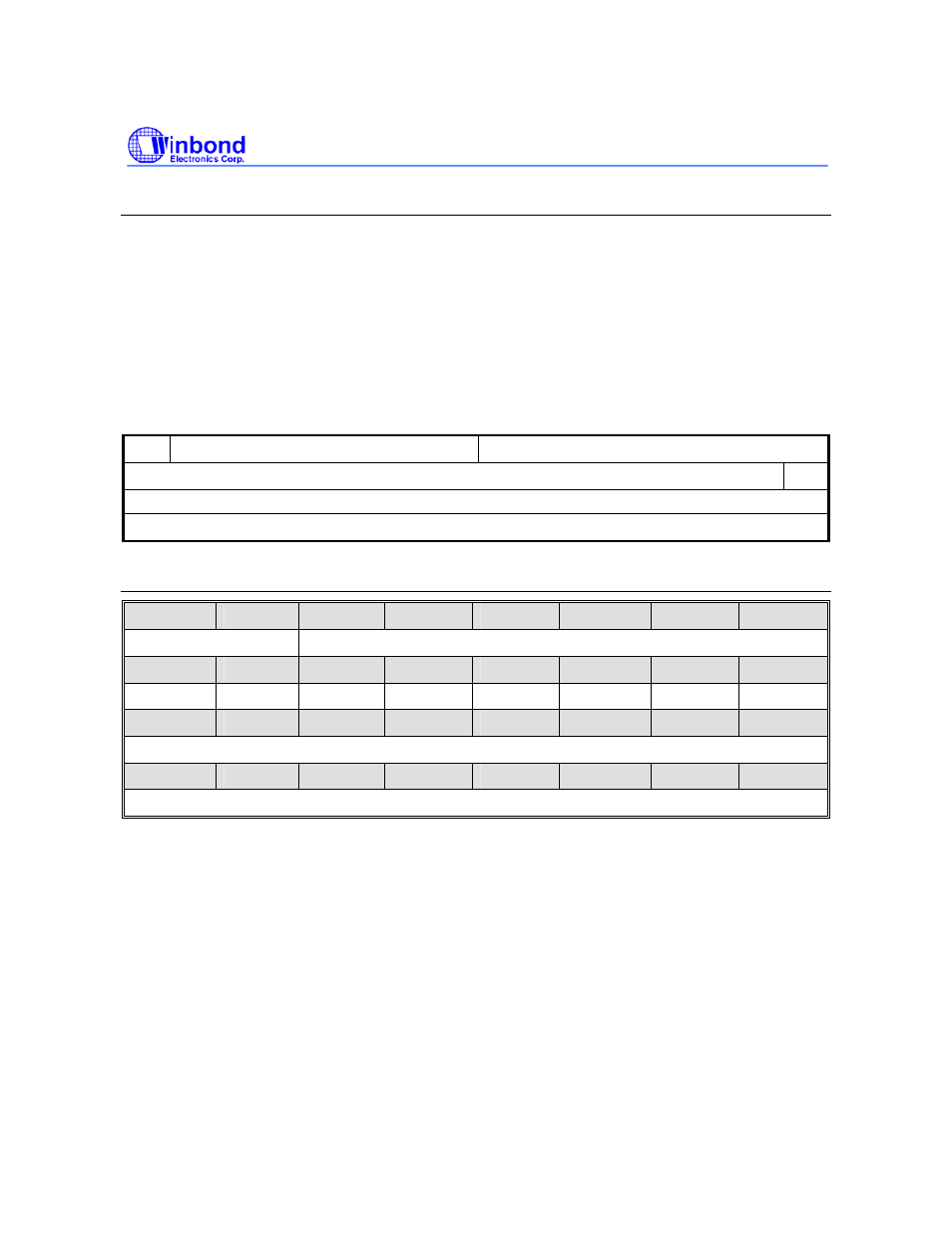

EMC Descriptors

A link-list data structure named as descriptor is used to keep the control, status and data

information of each frame. Through the descriptor, CPU and EMC exchange the information for frame

reception and transmission.

Two different descriptors are defined in W90P710. One named as Rx descriptor for frame

reception and the other names as Tx descriptor for frame transmission. Each Rx descriptor consists of

four words. There is much information kept in the descriptors and details are described as below.

6.5.1.1

Rx Buffer Descriptor

3

1

3

0

2

9

1

6

1

5

0

O

Rx Status

Receive Byte Count

Receive Buffer Starting Address

BO

Reserved

Next Rx Descriptor Starting Address

Rx Descriptor Word 0

31

30

29

28

27

26

25

24

Owner Reserved

23

22

21

20

19

18

17

16

Reserved RP ALIE RXGD PTLE Reserved

CRCE RXINTR

15

14

13

12

11

10

9

8

RBC

7

6

5

4

3

2

1

0

RBC

Owner [31:30]: Ownership

The ownership field defines which one, the CPU or EMC, is the owner of each Rx descriptor. Only the

owner has right to modify the Rx descriptor and the others can read the Rx descriptor only.

00: The owner is CPU

01: Undefined

10: The owner is EMC

11: Undefined

If the O=2’b10 indicates the EMC RxDMA is the owner of Rx descriptor and the Rx descriptor is

available for frame reception. After the frame reception completed, if the frame needed NAT

translation, EMC RxDMA modify ownership field to 2’b11. Otherwise, the ownership field will be

modified to 2’b00.