Rainbow Electronics W90P710CDG User Manual

Page 263

W90P710CD/W90P710CDG

Publication Release Date: September 19, 2006

- 263 -

Revision B2

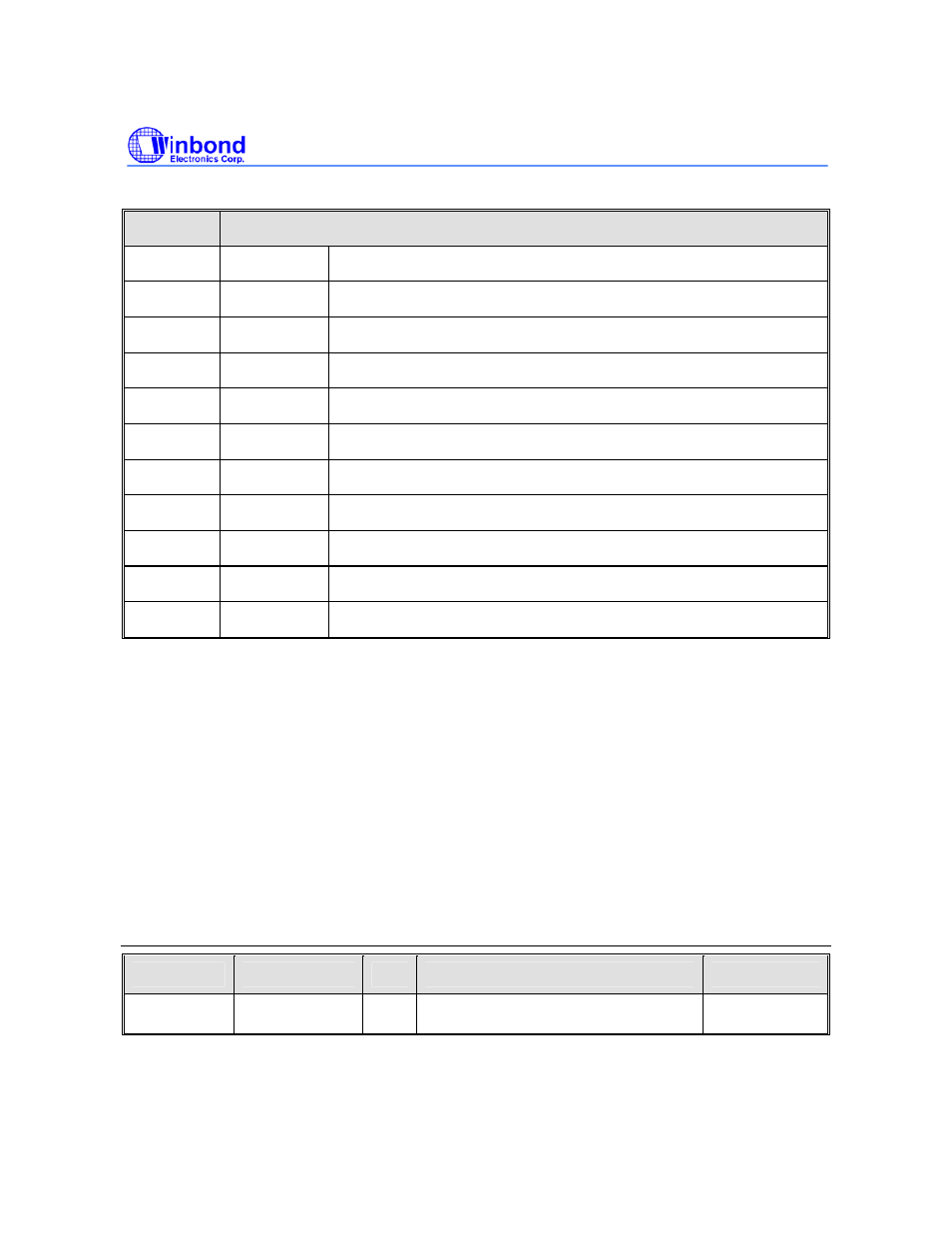

BITS

DESCRIPTIONS

[31:20] Reserved Reserved

[18]

UNDRIS2

FIFO2 have no data for output to Panel

[17]

UNDRIS1

FIFO1 have no data for output to Panel

[16]

AHBERIS

AHB master bus error status

[15:6] Reserved Reserved

[5]

HSIS

Timing Generator output a HSYNC pulse

[4]

VSIS

Timing Generator output a VSYNC pulse

[3]

VLFINIS2

FIFO2 transfer one line stream complete

[2]

VFFINIS2

FIFO2 transfer one frame stream complete

[1]

VLFINIS1

FIFO1 transfer one line stream complete

[0]

VFFINIS1

FIFO1 transfer one frame stream complete

LCD Controller is an AHB Master at AMBA and fetching video data from an AHB Slave such as SDRAM

or FLASH memory. If AHB Slave response ERROR for LCD Controller’s data request, AHBERIS will be

set.

If the data rate of output to LCD Panel is too fast and the data rate of fetch data from AMBA is too slow;

there are no data in FIFO for LCD Panel’s request, UNDRISx will be set. LCD Timing Generation register

need to be re-configured.

HSIS and VSIS provide information for firmware to know the status of LCD Panel.

VLFINISx and VFFINISx provide information for firmware to know how much data FIFO have fetched.

LCD Interrupt Clear Register (LCDINTC)

REGISTER

ADDRESS

R/W

DESCRIPTION

RESET VALUE

LCDINTC

0xFFF0_800C

W

LCD interrupt clear

0x0000_0000