Rainbow Electronics W90P710CDG User Manual

Page 483

W90P710CD/W90P710CDG

- 484 -

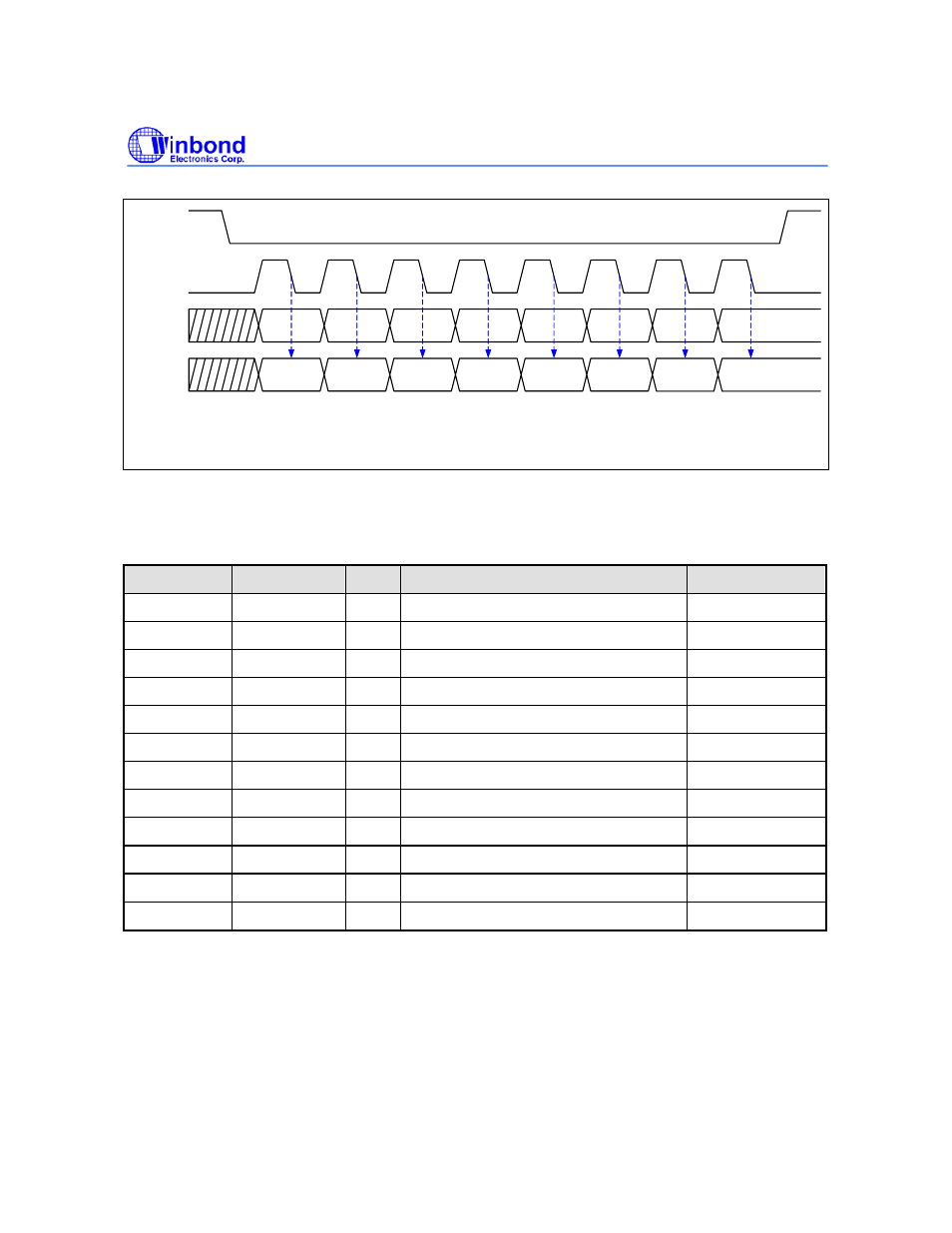

mw_ss_o

mw_sclk_o

mw_so_o

mw_si_i

CNTRL[LSB]=1, CNTRL[Tx_NUM]=0x0, CNTRL[Tx_BIT_LEN]=0x08,

CNTRL[Tx_NEG]=0, CNTRL[Rx_NEG]=1, SSR[SS_LVL]=0

MSB

(Tx[7])

LSB

(Tx[0])

MSB

(Rx[7])

LSB

(Rx[0])

Tx[1]

Tx[2]

Tx[3]

Tx[4]

Tx[5]

Tx[6]

Rx[1]

Rx[2]

Rx[3]

Rx[4]

Rx[5]

Rx[6]

Fig. 6.19.1.2 Alternate Phase SCLK Clock Timing

6.19.2 USI Registers Map

R: read only, W: write only, R/W: both read and write

REGISTER

ADDRESS

R/W

DESCRIPTION

RESET VALUE

USI_CNTRL 0xFFF8_6200 R/W

Control and Status Register

0x0000_0004

USI_DIVIDER 0xFFF8_6204 R/W

Clock Divider Register

0x0000_0000

USI_SSR 0xFFF8_6208

R/W

Slave

Select Register

0x0000_0000

Reserved 0xFFF8_620C

N/A

Reserved

N/A

USI_Rx0

0xFFF8_6210

R

Data Receive Register 0

0x0000_0000

USI_Rx1

0xFFF8_6214

R

Data Receive Register 1

0x0000_0000

USI_Rx2

0xFFF8_6218

R

Data Receive Register 2

0x0000_0000

USI_Rx3

0xFFF8_621C

R

Data Receive Register 3

0x0000_0000

USI_Tx0

0xFFF8_6210

W

Data Transmit Register 0

0x0000_0000

USI_Tx1

0xFFF8_6214

W

Data Transmit Register 1

0x0000_0000

USI_Tx2

0xFFF8_6218

W

Data Transmit Register 2

0x0000_0000

USI_Tx3

0xFFF8_621C

W

Data Transmit Register 3

0x0000_0000

NOTE 1

: When software programs CNTRL, the GO_BUSY bit should be written last.