Rainbow Electronics W90P710CDG User Manual

Page 62

W90P710CD/W90P710CDG

- 62 -

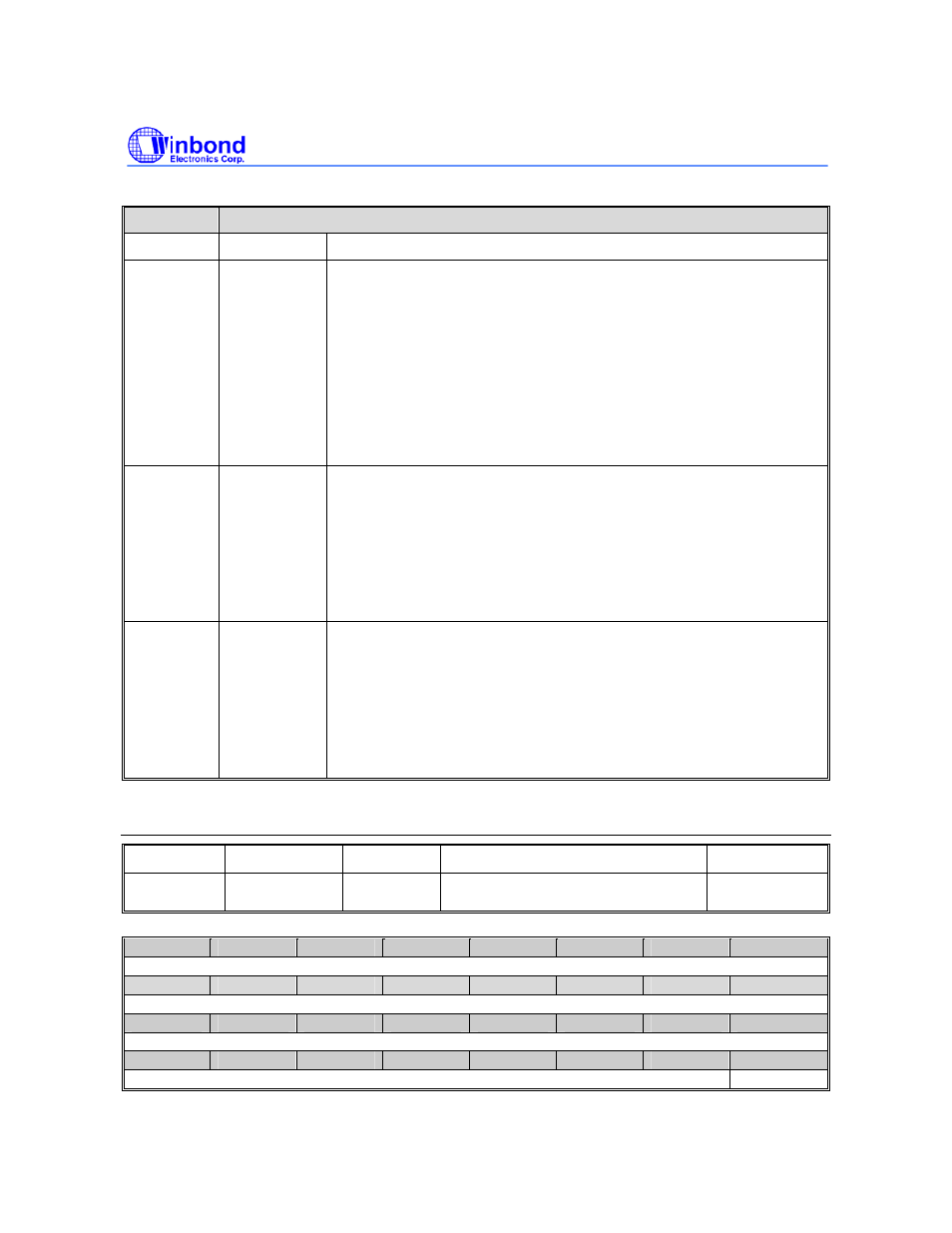

BITS

DESCRIPTION

[31:3] RESERVED

[2] MIDLE

Memory controller IDLE enable

Setting both MIDLE and IDLE bits HIGH will let memory controller

enter IDLE mode, the clock source of memory controller will be halted

while ARM CORE enter IDLE mode.

1=memory controller will be forced into IDLE mode, (clock of memory

controller will be halted), when IDLE bit is set.

0 = memory controller still active when IDLE bit is set.

NOTE: Software must let SDRAM enter self-refresh mode before

enable this function because SDRAM MCLK will be stopped.

[1] PD

Power down enable

Setting this bit HIGH will let W90P710 enter power saving mode. The

clock source 15M crystal oscillator and PLLs are stopped to generate

clock. User can use nIRQ[3:0], keypad and external RESET to wakeup

W90P710.

1 = Enable power down

0 = Disable

[0] IDLE

IDLE mode enable

Setting this bit HIGH will let ARM Core enter power saving mode. The

peripherals can still keep working if the clock enable bit in CLKSEL is

set. Any nIRQ or nFIQ to ARM Core will let ARM CORE to exit IDLE

state.

1 = IDLE mode

0 = Disable

USB Transceiver Control Register (USBTXRCON)

REGISTER ADDRESS

R/W

DESCRIPTION

RESET

VALUE

USBTXRCO

N

0xFFF0_0030 R/W USB Transceiver Control Register

0x0000_0000

31

30

29

28

27

26

25

24

RESERVED

23

22

21

20

19

18

17

16

RESERVED

15

14

13

12

11

10

9

8

RESERVED

7

6

5

4

3

2

1

0

RESERVED

USBHnD