Rainbow Electronics W90P710CDG User Manual

Page 144

W90P710CD/W90P710CDG

- 144 -

Continued.

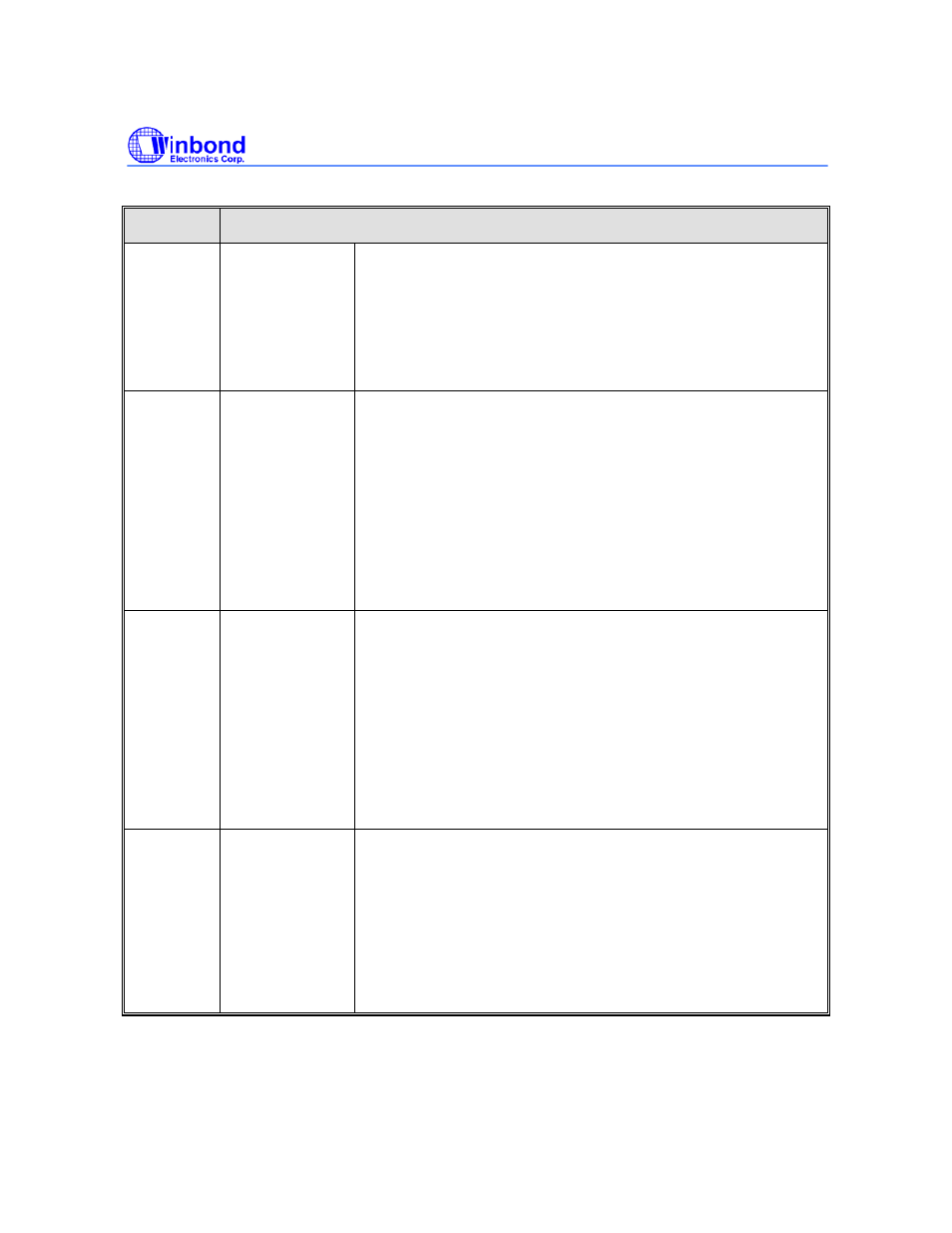

BITS

DESCRIPTIONS

[4] RXGD

The Receive Good Interrupt high indicates the frame reception

has completed.

If the RXGD is high and EnRXGD of MIEN register is enabled, the

RxINTR will be high. Write 1 to this bit clears the RXGD status.

1’b0: The frame reception has not complete yet.

1’b1: The frame reception has completed.

[3] PTLE

The Packet Too Long Interrupt high indicates the length of the

incoming packet is greater than 1518 bytes and the incoming

packet is dropped. If the ALP of MCMDR register is set, the long

packet will be regarded as a good packet and PTLE will not be

set.

If the PTLE is high and EnPTLE of MIEN register is enabled, the

RxINTR will be high. Write 1 to this bit clears the PTLE status.

1’b0: The incoming frame is not a long frame or S/W wants to

receive a long frame.

1’b1: The incoming frame is a long frame and dropped.

[2]

RXOV

The Receive FIFO Overflow Interrupt high indicates the RxFIFO

overflow occurred during packet reception. While the RxFIFO

overflow occurred, the EMC drops the current receiving packer. If

the RxFIFO overflow occurred often, it is recommended that

modify RxFIFO threshold control, the RxTHD of FFTCR register,

to higher level.

If the RXOV is high and EnRXOV of MIEN register is enabled, the

RxINTR will be high. Write 1 to this bit clears the RXOV status.

1’b0: No RxFIFO overflow occurred during packet reception.

1’b0: RxFIFO overflow occurred during packet reception.

[1] CRCE

The CRC Error Interrupt high indicates the incoming packet

incurred the CRC error and the packet is dropped. If the AEP of

MCMDR register is set, the CRC error packet will be regarded as

a good packet and CRCE will not be set.

If the CRCE is high and EnCRCE of MIEN register is enabled, the

RxINTR will be high. Write 1 to this bit clears the CRCE status.

1’b0: The frame doesn’t incur CRC error.

1’b1: The frame incurred CRC error.