No nr nf 1 ∗ ∗ f, Clock select register (clksel) – Rainbow Electronics W90P710CDG User Manual

Page 53

W90P710CD/W90P710CDG

Publication Release Date: September 19, 2006

- 53 -

Revision B2

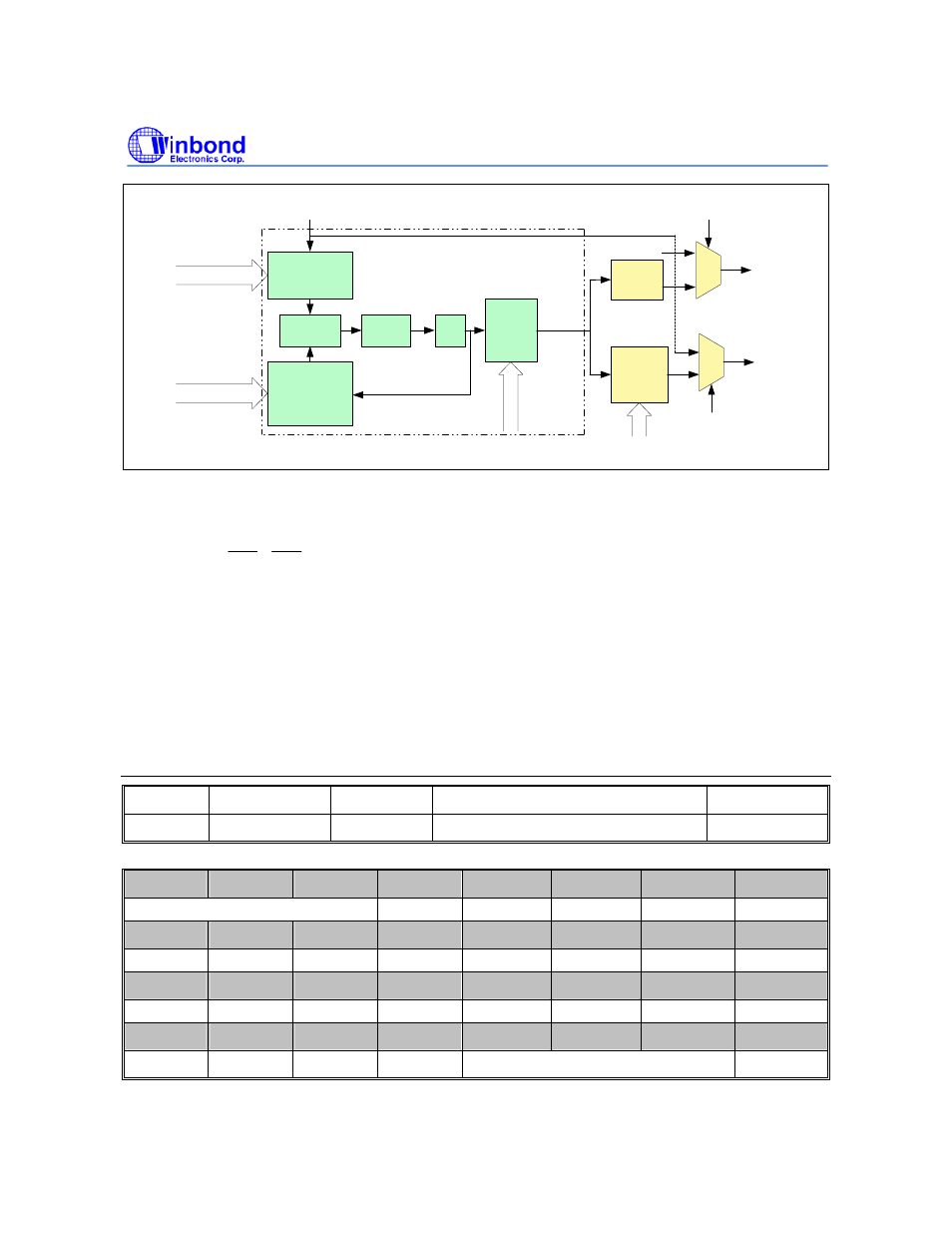

Input Divider

(NR)

PFD

Feedback

Divider

(NF)

Charge

Pump

VCO

Output

Divider

(NO)

Clock

Divider

&

Selector

EXTAL

ECLKS

OTDV[1:0]

CLKS[2:0]

1

0

PLL

Internal

System

Clock

INDV[4:0]

FBDV[8:0]

48MHz

Gen

480MHz

0

1

USBCKS

USB

Module

FIN

FOUT

GP0

Fig 6.2.8.1 System PLL block diagram

The formula of output clock of PLL is:

F

OUT

= F

IN

NO

NR

NF

1

∗

∗

F

OUT:

Output clock of Output Divider

F

IN:

External clock into the Input Divider

NR:Input divider value (NR = INDV + 2)

NF:Feedback divider value (NF = FBDV + 2)

NO:Output divider value (NO = OTDV)

Clock Select Register (CLKSEL)

REGISTER ADDRESS

R/W

DESCRIPTION

RESET

VALUE

CLKSEL

0xFFF0_000C R/W Clock Select Register

0x1FFF_7FX8

31

30

29

28

27

26

25

24

RESERVED PS2

KPI

SCH1

SCH0

SSP

23

22

21

20

19

18

17

16

UART3 UART2 UART1 I2C1

I2C0

RTC

PWM

AC97

15

14

13

12

11

10

9

8

USBCKS USBD GDMA

SD

LCD

EMC RESERVED WDT

7

6

5

4

3

2

1

0

USBH TIMER UART ECLKS

CLKS

RESET