Rainbow Electronics W90P710CDG User Manual

Page 450

W90P710CD/W90P710CDG

- 450 -

Contiuned

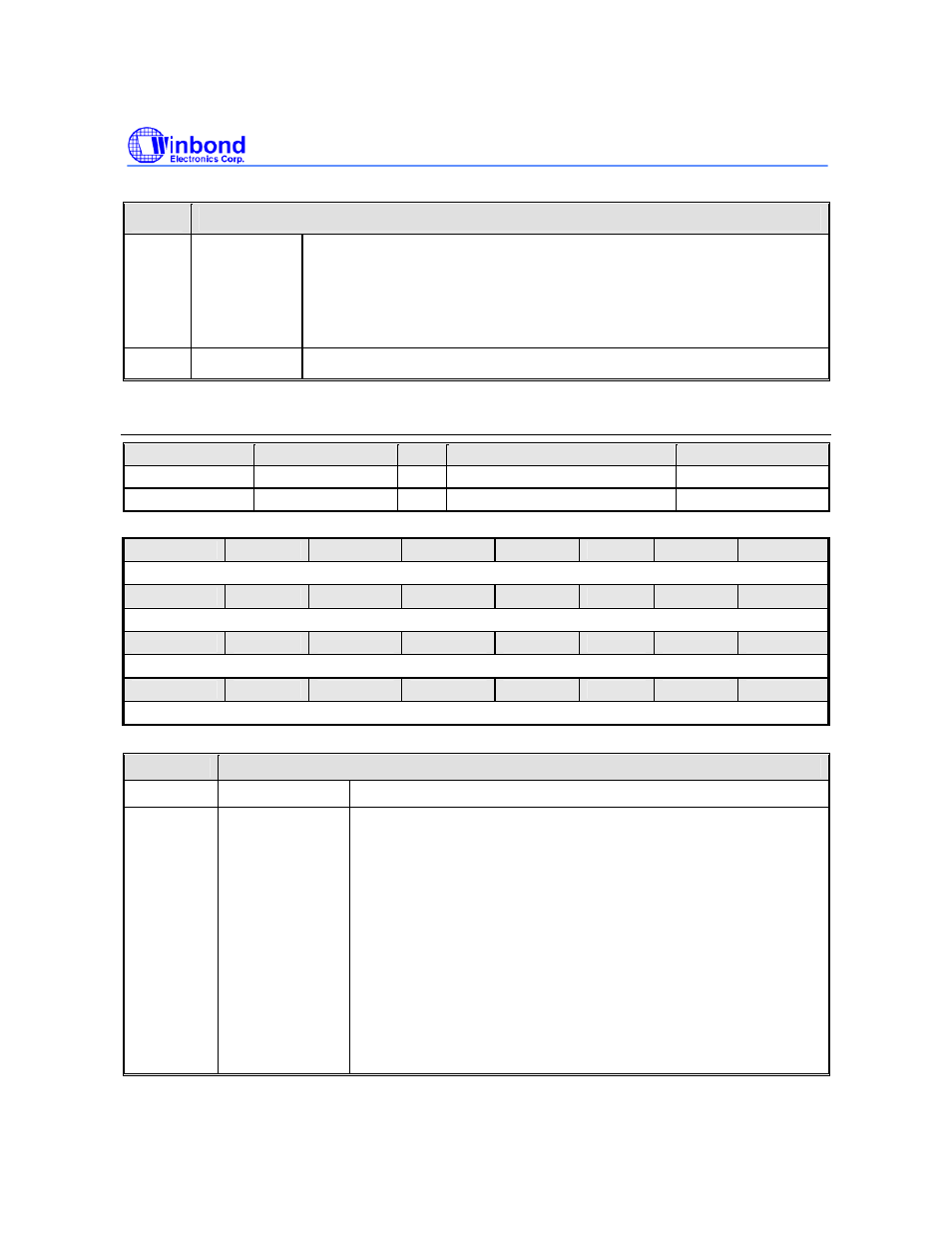

BITS

DESCRIPTIONS

[2]

CDP

Card Detect Polarity.

We can use the CDP bit to choose the card present input polarity for

different socket application.

0 : the input high means card is present.

1 : the input low means card is present.

[1:0]

RESERVED -

Smart Card Host Clock Base Register (SCHI_CBR)

REGISTER

ADDRESS

R/W

DESCRIPTION

RESET VALUE

SCHI_CBR0 0xFFF8_5010

R/W Clock base Register 0

0x0000_000C

SCHI_CBR1 0xFFF8_5810

R/W Clock base Register 1

0x0000_00OC

BITS

DESCRIPTIONS

[31:8]

RESERVED -

[7:0]

CBR

Clock Base value.

It specifies number of internal sampling clock pulses for a data bit.

Default to be 0Ch.

This register combining with BLH and BLL (baud rate latches)

determine internal sampling clock frequency. For example, CBR

defaults to be 0Ch and BLH, BLL default to be 1Fh which mean

SCCLK clock frequency is 372 (12 x 31) times of internal sampling

clock frequency. The default values of CBR, BLH and BLL are

corresponding to default values of transmission factors F and D

specified in ISO/IEC 7816-3. The value of 0Ch of CBR means

there're 12 sampling clock pulses to detect a 1-etu (elementary

time unit) data bit on SCIO signal. It is recommended that user

sets CBR to be around 16 to maintain better data integrity and

transmission stability.

31

30

29

28

27

26

25

24

RESERVED

23

22

21

20

19

18

17

16

RESERVED

15

14

13

12

11

10

9

8

RESERVED

7

6

5

4

3

2

1

0

8-bit clock base Data