Rainbow Electronics W90P710CDG User Manual

Page 167

W90P710CD/W90P710CDG

Publication Release Date: September 19, 2006

- 167 -

Revision B2

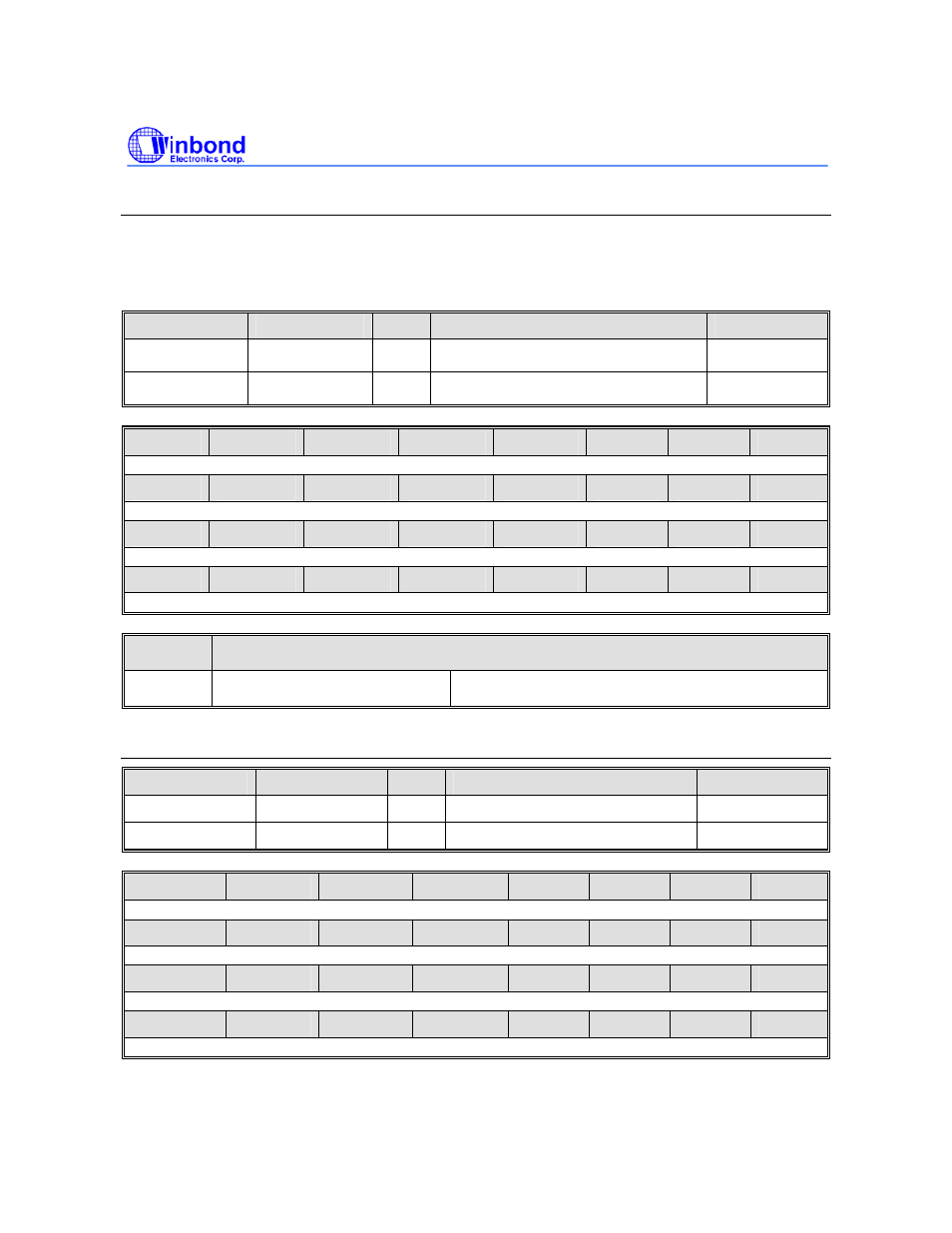

Channel 0/1 Destination Base Address Register (GDMA_DSTB0, DMA_DSTB1)

Channel 0/1 Destination Base Address Register (GDMA_DSTB0, GDMA_DSTB1)

The GDMA channel starts writing its data to the destination address as defined in this destination base

address register. During a block transfer, the GDMA determines successive destination addresses by

adding to or subtracting from the destination base address.

REGISTER

ADDRESS

R/W

DESCRIPTION

RESET VALUE

GDMA_DSTB0 0xFFF0_4008 R/W

Channel 0 Destination Base Address

Register

0x0000_0000

GDMA_DSTB1 0xFFF0_4028 R/W

Channel 1 Destination Base Address

Register

0x0000_0000

31

30

29

28

27

26

25

24

DST_BASE_ADDR [31:24]

23

22

21

20

19

18

17

16

DST_BASE_ADDR [23:16]

15

14

13

12

11

10

9

8

DST_BASE_ADDR [15:8]

7

6

5

4

3

2

1

0

DST_BASE_ADDR [7:0]

BITS

DESCRIPTIONS

[31:0] DST_BASE_ADDR

32-bit

Destination Base Address

Channel 0/1 Transfer Count Register (GDMA_TCNT0, GDMA_TCNT1)

REGISTER

ADDRESS

R/W

DESCRIPTION

RESET VALUE

GDMA_TCNT0

0xFFF0_400C R/W

Channel 0 Transfer Count Register

0x0000_0000

GDMA_TCNT1

0xFFF0_402C R/W

Channel 1 Transfer Count Register

0x0000_0000

31

30

29

28

27

26

25

24

Reserved

23

22

21

20

19

18

17

16

TFR_CNT [23:16]

15

14

13

12

11

10

9

8

TFR_CNT [15:8]

7

6

5

4

3

2

1

0

TFR_CNT [7:0]