Rainbow Electronics W90P710CDG User Manual

Page 57

W90P710CD/W90P710CDG

Publication Release Date: September 19, 2006

- 57 -

Revision B2

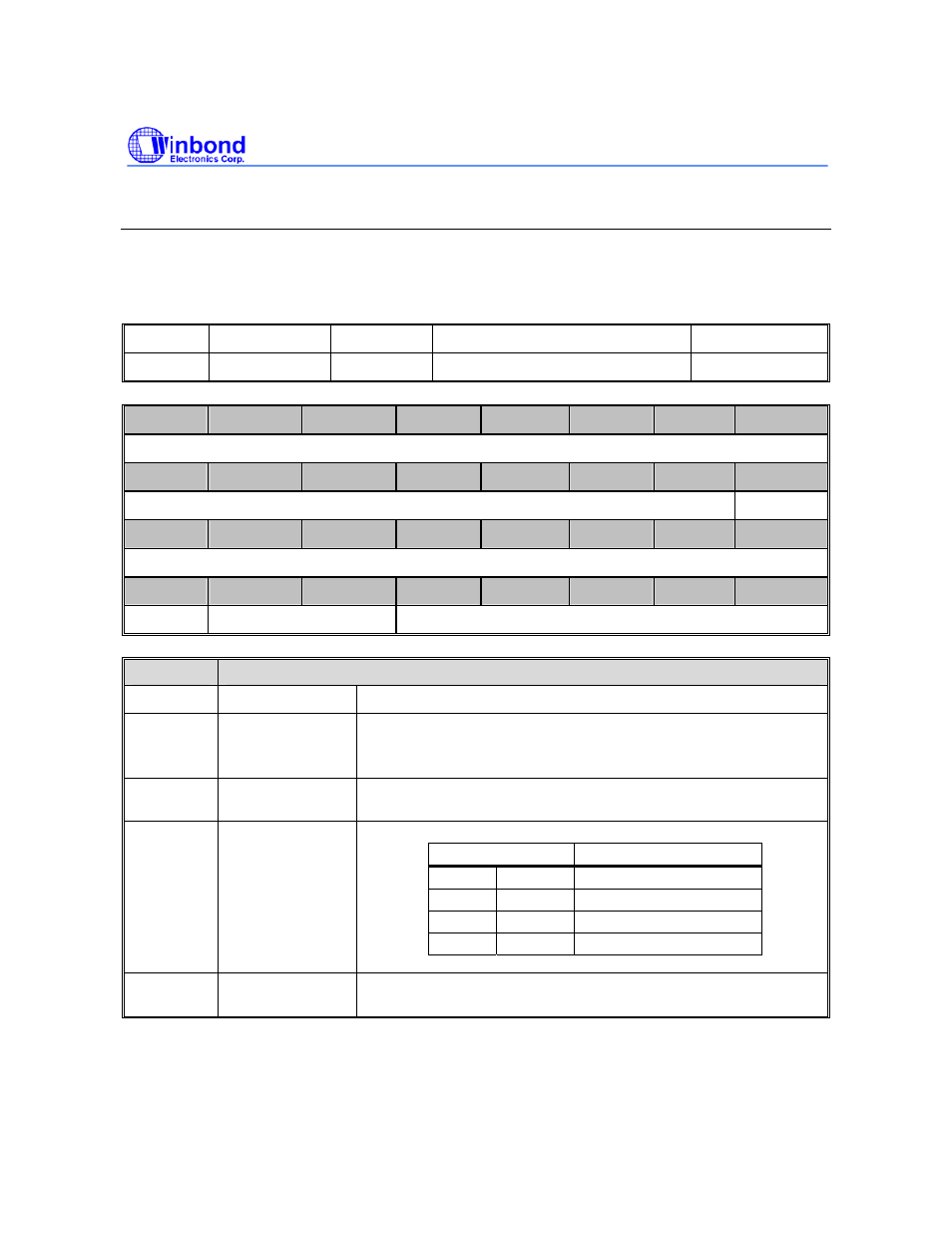

PLL Control Register 1(PLLCON1)

W90P710 provides extra PLL for LCD controller programmable pixel clock and provide 12.288/16.934

MHz clock source to Audio Controller. It uses the same 15MHz crystal clock input source with system

PLL mentioned above.

REGISTER ADDRESS

R/W

DESCRIPTION

RESET

VALUE

PLLCON1 0xFFF0_0010 R/W

PLL Control Register 1

0x0001_0000

31

30

29

28

27

26

25

24

RESERVED

23

22

21

20

19

18

17

16

RESERVED PWDEN1

15

14

13

12

11

10

9

8

FBDV1

7

6

5

4

3

2

1

0

FBDV1 OTDV1

INDV1

BITS

DESCRIPTION

[31:17] RESERVED

-

[16] PWDEN1

PLL1 power down enable

0 = PLL1 is in normal mode

1 = PLL1 is in power down mode (default)

[15:7] FBDV1

PLL1 VCO output clock feedback divider

Feedback Divider divides the output clock from VCO of PLL1.

[6:5] OTDV1

PLL1 output clock divider

OTDV1 [6:5]

Divided by

0 0

1

0 1

2

1 0

2

1 1

4

[4:0]

INDV1

PLL1 input clock divider

Input divider divides the input reference clock into the PLL1.