Rainbow Electronics W90P710CDG User Manual

Page 97

W90P710CD/W90P710CDG

Publication Release Date: September 19, 2006

- 97 -

Revision B2

Continued.

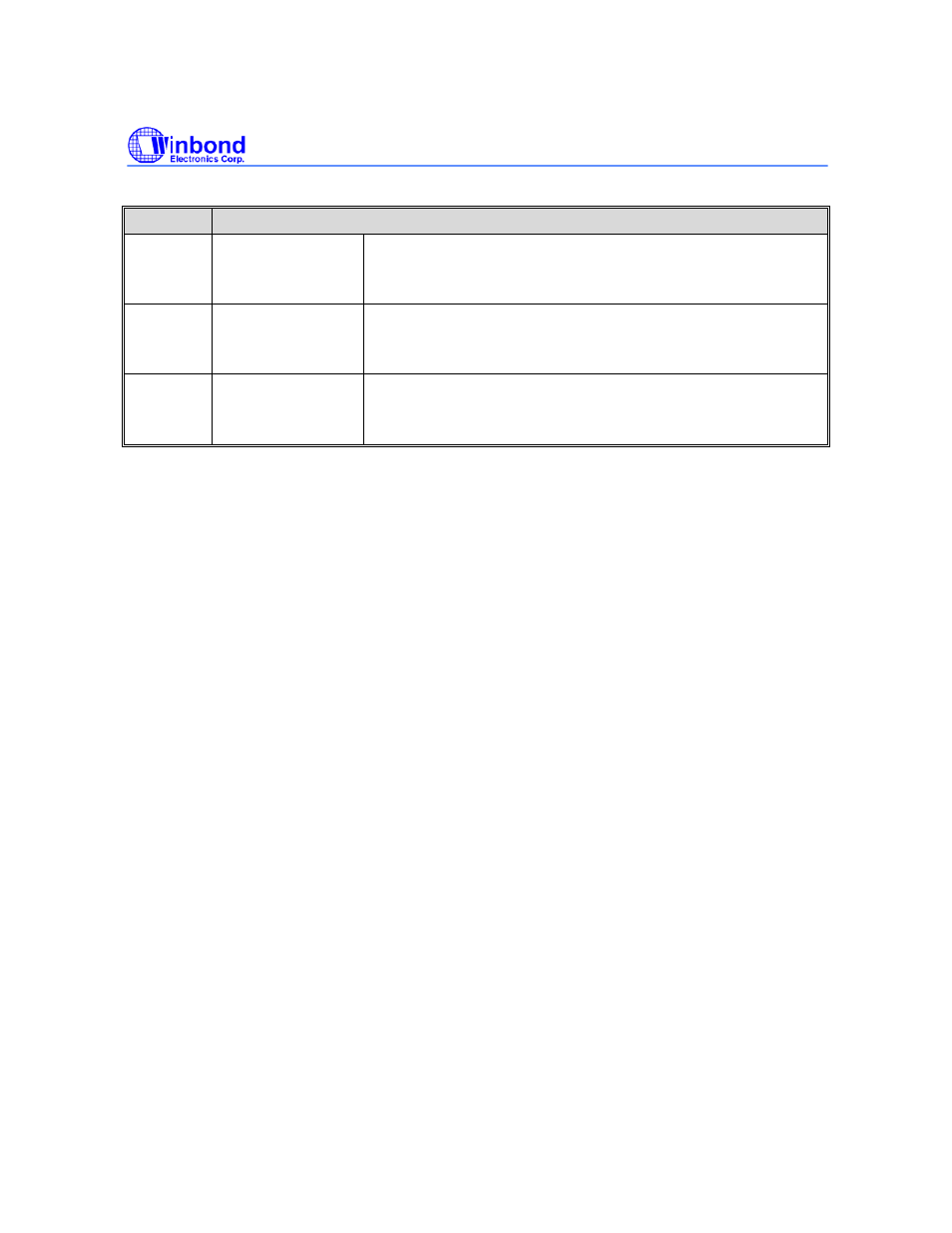

BITS

DESCRIPTION

[2] BFAIL2

BIST test fail for data cache ram way 0

If this bit equals to “1”, it indicates the data cache ram for way 0 is

tested fail by BIST. “0” means the test is passed.

[1] BFAIL1

BIST test fail for instruction cache ram way 1

If this bit equals to “1”, it indicates the instruction cache ram for

way 1 is tested fail by BIST. “0” means the test is passed.

[0] BFAIL0

BIST test fail for instruction cache ram way 0

If this bit equals to “1”, it indicates the instruction cache ram for

way 0 is tested fail by BIST. “0” means the test is passed.

6.5 Ethernet MAC Controller

Overview

The W90P710 provides an Ethernet MAC Controller (EMC) for LAN application. This EMC has its

DMA controller, transmit FIFO, and receive FIFO.

The Ethernet MAC controller consists of IEEE 802.3/Ethernet protocol engine with internal CAM

function for Ethernet MAC address recognition, Transmit-FIFO, Receive-FIFO, TX/RX state machine

controller and status controller. The EMC only supports RMII (Reduced MII) interface to connect with

PHY operating on 50MHz REF_CLK.

Features

y

Supports IEEE Std. 802.3 CSMA/CD protocol.

y

Supports both half and full duplex for 10M/100M bps operation.

y

Supports RMII interface.

y

Supports MII Management function.

y

Supports pause and remote pause function for flow control.

y

Supports long frame (more than 1518 bytes) and short frame (less than 64 bytes) reception.

y

Supports 16 entries CAM function for Ethernet MAC address recognition.

y

Supports internal loop back mode for diagnostic.

y

Supports 256 bytes embedded transmit and receive FIFO.

y

Supports DMA function.