Rainbow Electronics W90P710CDG User Manual

Page 59

W90P710CD/W90P710CDG

Publication Release Date: September 19, 2006

- 59 -

Revision B2

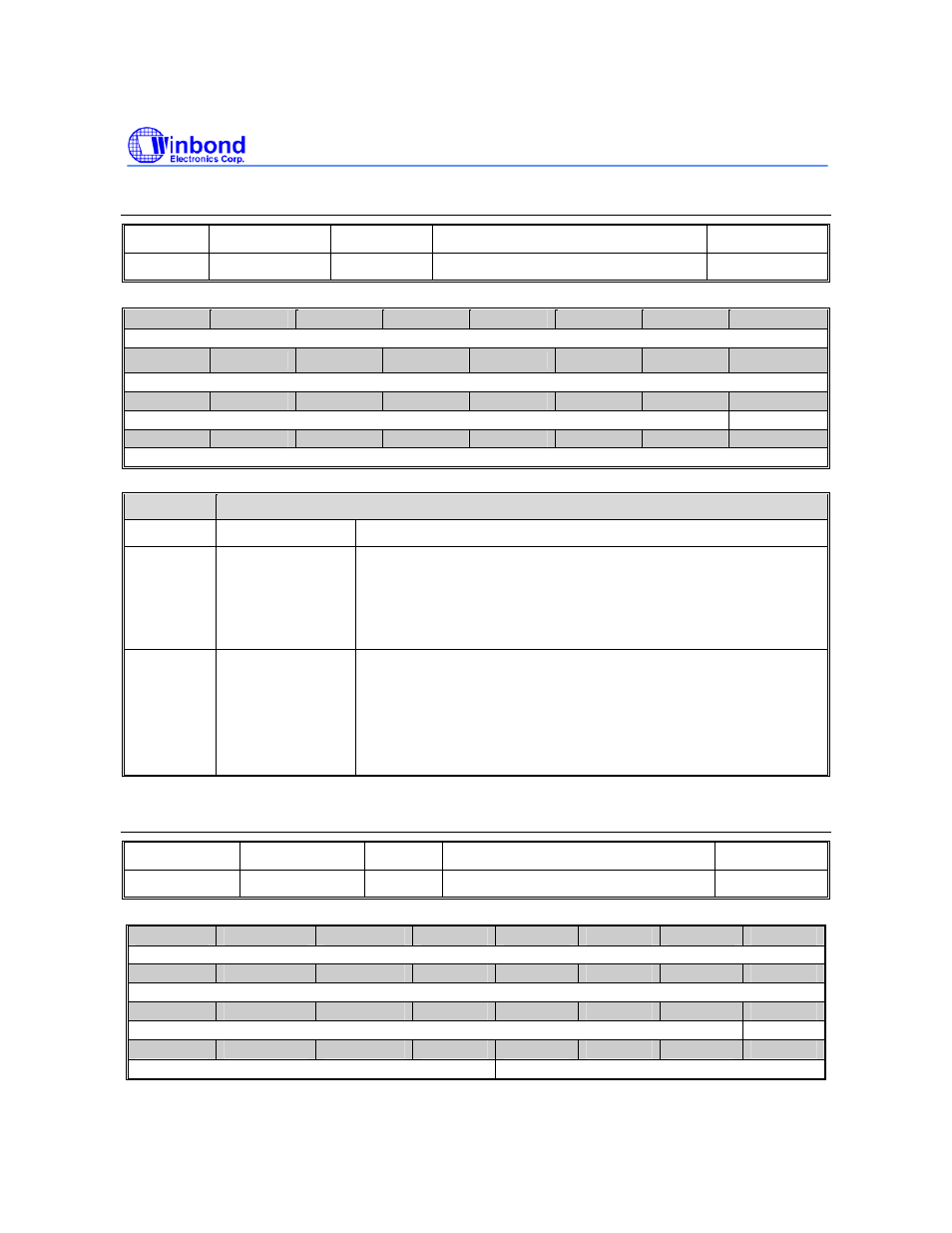

IIS Clock Control Register (I2SCKCON)

REGISTER ADDRESS

R/W

DESCRIPTION

RESET

VALUE

I2SCKCON 0xFFF0_0014 R/W

I2S PLL clock Control Register

0x0000_0000

31

30

29

28

27

26

25

24

RESERVED

23

22

21

20

19

18

17

16

RESERVED

15

14

13

12

11

10

9

8

RESERVED IISPLLEN

7

6

5

4

3

2

1

0

PRESCALE

BITS

DESCRIPTION

[31:9] RESERVED

-

[8] I2SPLLEN

IIS PLL clock source enable

Set this bit will enable PLL1 clock output to audio I2S clock input.

1 = Enable PLL1 clock source for audio I2S

0 = Disable PLL1 clock source for audio I2S

[7:0] PRESCALE

The PLL1 is shared with LCD controller, if both the LCD and I2S are

using the PLL at the same time, software can using this prescaler

to generate an appropriate clock nearly 12.288M or 16.934M. The

clock is generated as below, and if PRESCALE =0, the

PLL_AUDIO is the same frequency as FOUT “PLL_AUDIO =

PLL_FOUT/(PRESCALE +1)”

IRQ Wakeup Control Register (IRQWAKECON)

REGISTER ADDRESS R/W

DESCRIPTION

RESET

VALUE

IRQWAKECON 0xFFF0_0020 R/W IRQ Wakeup Control Register

0x0000_0000

31

30

29

28

27

26

25

24

RESERVED

23

22

21

20

19

18

17

16

RESERVED

15

14

13

12

11

10

9

8

RESERVED

7

6

5

4

3

2

1

0

IRQWAKEUPPOL IRQWAKEUPEN