Rainbow Electronics W90P710CDG User Manual

Page 487

W90P710CD/W90P710CDG

- 488 -

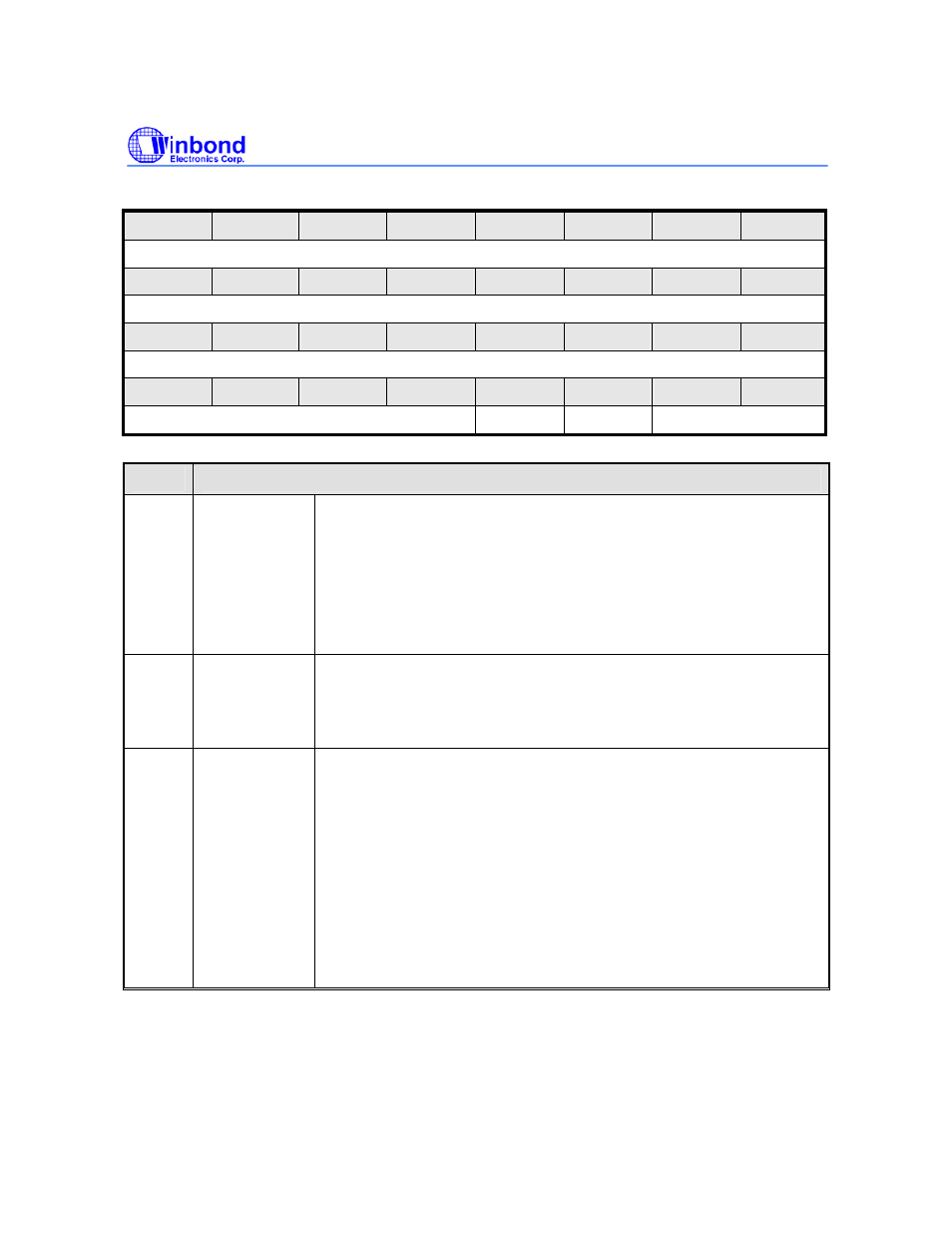

31

30

29

28

27

26

25

24

Reserved

23

22

21

20

19

18

17

16

Reserved

15

14

13

12

11

10

9

8

Reserved

7

6

5

4

3

2

1

0

Reserved

ASS

SS_LVL

SSR[1:0]

BITS

DESCRIPTIONS

[3]

ASS

Automatic Slave Select

0 = If this bit is cleared, slave select signals are asserted and de-

asserted by setting and clearing related bits in SSR register.

1 = If this bit is set, usi_ss_o signals are generated automatically. It

means that device/slave select signal, which is set in SSR register is

asserted by the USI controller when transmit/receive is started by

setting CNTRL[GO_BUSY], and is de-asserted after every

transmit/receive is finished.

[2]

SS_LVL

Slave Select Active Level

It defines the active level of device/slave select signal (usi_ss_o).

0 = The usi_ss_o slave select signal is active Low.

1 = The usi_ss_o slave select signal is active High.

[1:0]

SSR

Slave Select Register

If SSR[ASS] bit is cleared, writing 1 to any bit location of this field sets

the proper sui_ss_o line to an active state and writing 0 sets the line

back to inactive state.

If SSR[ASS] bit is set, writing 1 to any bit location of this field will select

appropriate sui_ss_o line to be automatically driven to active state for

the duration of the transmit/receive, and will be driven to inactive state

for the rest of the time. (The active level of usi_ss_o is specified in

SSR[SS_LVL]).

NOTE: This interface can only drive one device/slave at a given time.

Therefore, the slave select of the selected device must be set to its

active level before starting any read or write transfer.