Rainbow Electronics W90P710CDG User Manual

Page 194

W90P710CD/W90P710CDG

- 194 -

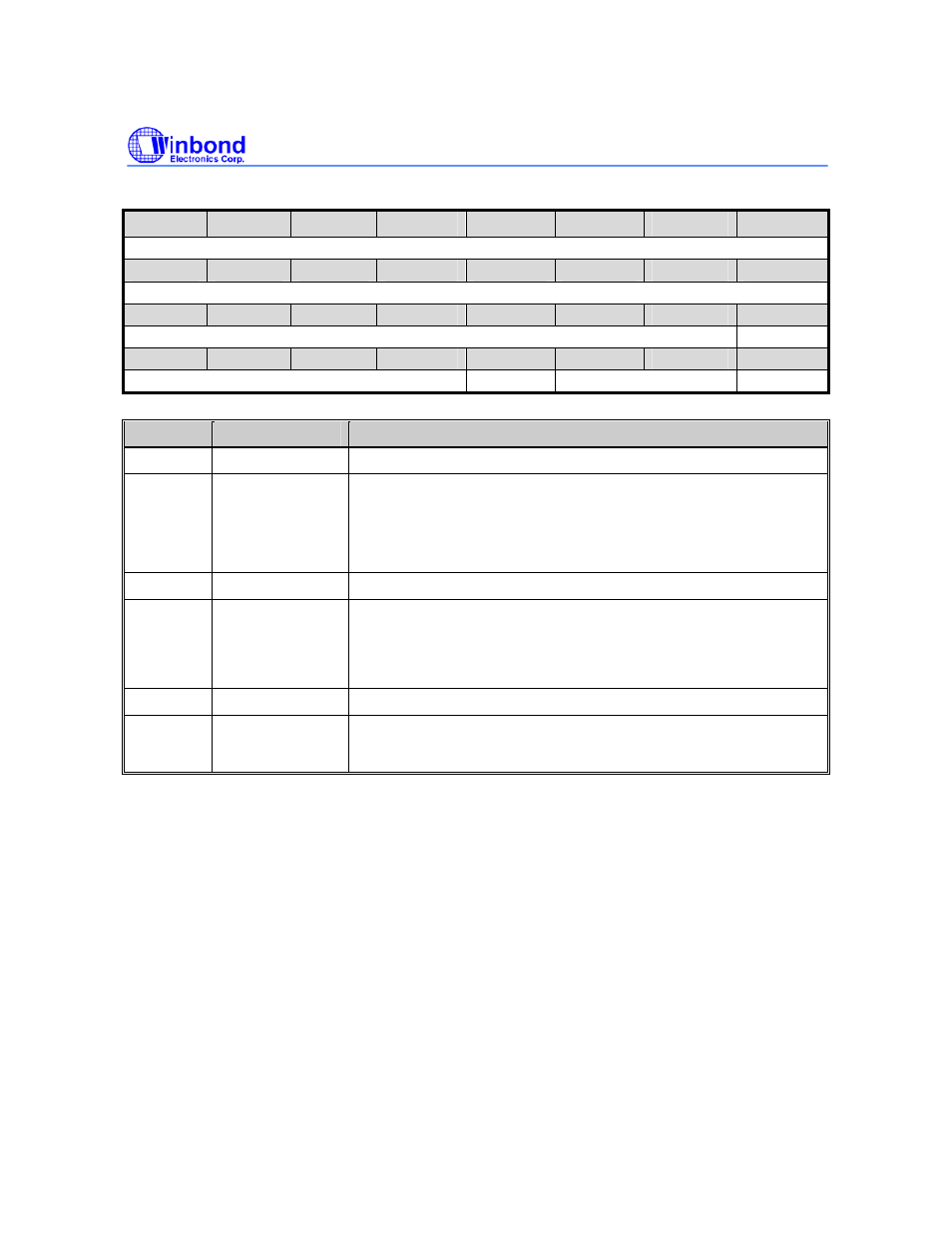

31

30

29

28

27

26

25

24

Reserved

23

22

21

20

19

18

17

16

Reserved

15

14

13

12

11

10

9

8

Reserved

SIEPD

7

6

5

4

3

2

1

0

Reserved

OVRCUR

Reserved

DBREG

BITS

BIT DESCRIPTION

[31:9]

Reserved

Reserved. Read/write 0

[8] SIEPD

SIE Pipeline Disable

When set, waits for all USB bus activity to complete prior to

returning completion status to the List Processor. This is a failsafe

mechanism to avoid potential problems with the clk_dr transition

between 1.5 MHz and 12 MHz.

[7:4]

Reserved

Reserved. Read/write 0

[3] OVRCURP

OVRCURP (over current indicator polarity)

When the OVRCURP bit is clear, the OVRCUR non-inverted to

input into USB host controller. In contrast, when the OVRCURP bit

is set, the OVRCUR inverted to input into USB host controller.

[2:1]

Reserved

Reserved. Read/write 0

[0] DBREG

Data Buffer Region 16

When set, the size of the data buffer region is 16 bytes. Otherwise, the

size is 32 bytes.

6.7.3 HCCA

6.7.4 Endpoint Descriptor

6.7.5 Transfer Descriptor

6.8 USB Device Controller

The USB controller interfaces the AHB bus and the USB bus. The USB controller contains both the

AHB master interface and AHB slave interface. CPU programs the USB controller through the AHB

slave interface. For IN or OUT transfer, the USB controller needs to write data to memory or read data

from memory through the AHB master interface. The USB controller also contains the USB

transceiver to interface the USB.