Rainbow Electronics W90P710CDG User Manual

Page 75

W90P710CD/W90P710CDG

Publication Release Date: September 19, 2006

- 75 -

Revision B2

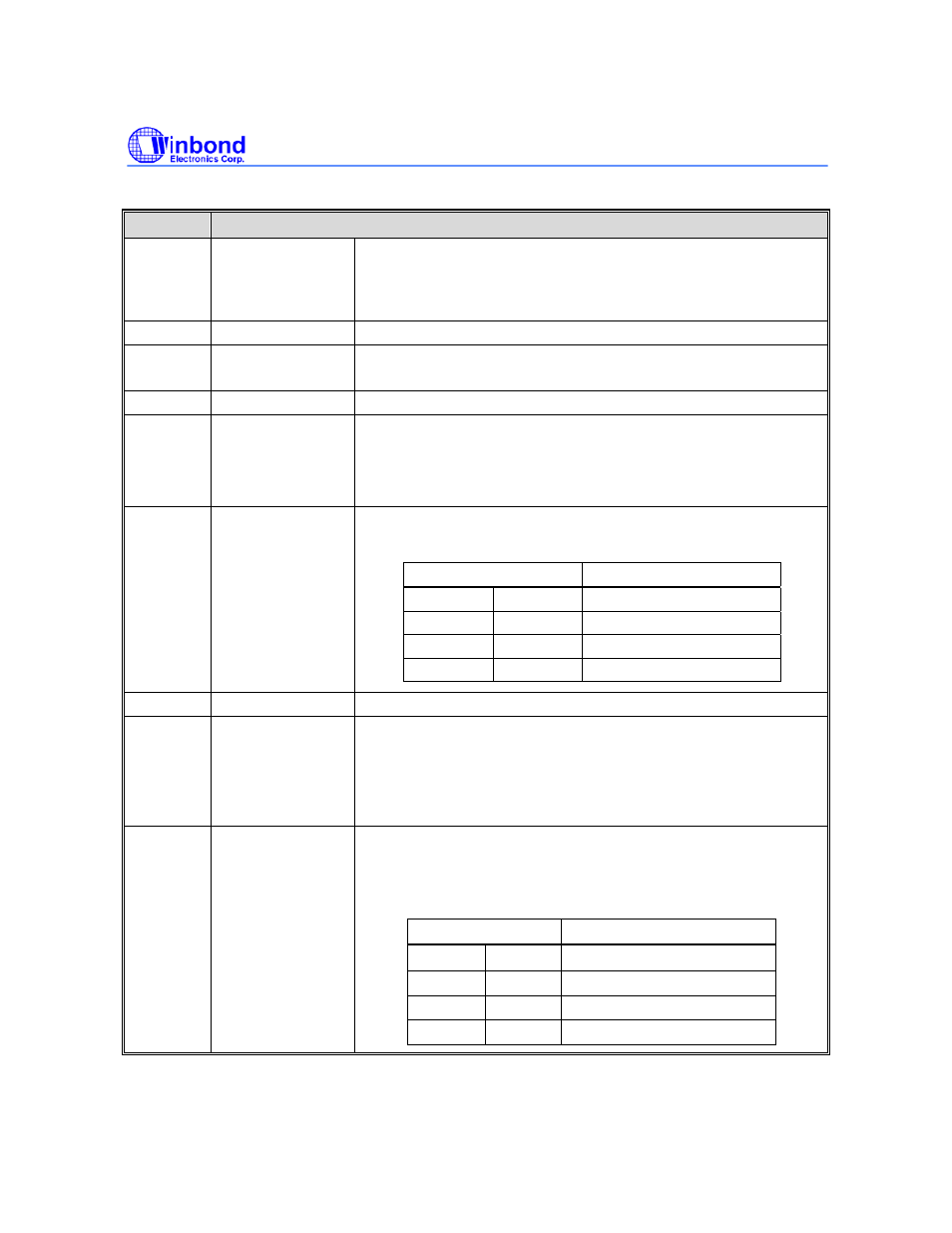

BITS

DESCRIPTION

[31:19] BASADDR

Base address pointer of SDRAM bank 0/1

The start address is calculated as SDRAM bank 0/1 base pointer

<< 18. The SDRAM base address pointer together with the “SIZE”

bits constitutes the whole address range of each SDRAM bank.

[18:16] RESERVED

-

[15] MRSET

SDRAM Mode register set command for SDRAM bank 0/1

This bit set will issue a mode register set command to SDRAM.

[14] RESERVED

-

[13] AUTOPR

Auto pre-charge mode of SDRAM for SDRAM bank 0/1

Enable the auto pre-charge function of external SDRAM bank 0/1

1= Auto pre-charge

0 = No auto pre-charge

[12:11] LATENCY

The CAS Latency of SDRAM bank 0/1

Defines the CAS latency of external SDRAM bank 0/1

LATENCY [12:11]

MCLK

0 0

1

0 1

2

1 0

3

1 1 REVERSED

[10:8] RESERVED

-

[7] COMPBK

Number of component bank in SDRAM bank 0/1

Indicates the number of component bank (2 or 4 banks) in external

SDRAM bank 0/1.

0 = 2 banks

1 = 4 banks

[6:5] DBWD

Data bus width for SDRAM bank 0/1

Indicates the external data bus width connect with SDRAM bank 0/1

If DBWD = 00, the assigned SDRAM access signal is not generated

i.e. disable.

DBWD [6:5]

Bits

0 0

Bank

disable

0 1

8-bit

(byte)

1 0 16-bit

(half-word)

1 1

32-bit

(word)