Rainbow Electronics W90P710CDG User Manual

Page 67

W90P710CD/W90P710CDG

Publication Release Date: September 19, 2006

- 67 -

Revision B2

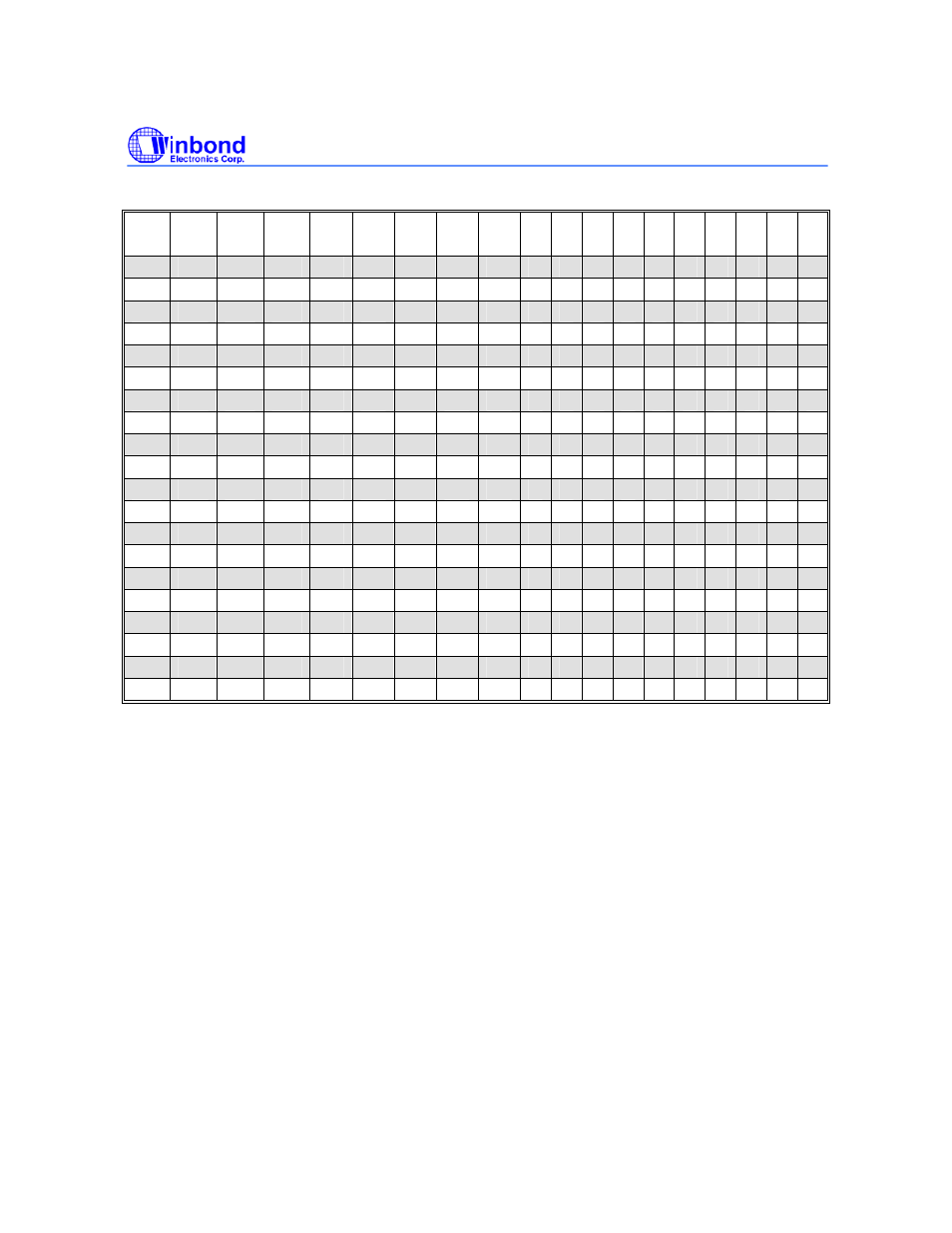

SDRAM Data Bus Width: 8-bit

Total

Type

R x C

R/C

A14

(BS1)

A13

(BS0)

A12

A11

A10

A9

A8

A7

A6

A5

A4 A3 A2 A1

A0

16M

2Mx8

11x9

R

**

9

**

9*

20

19

18

17

16

15

14

13

12

11

10

C

** 9 ** 9*

AP

23*

8

7

6

5

4

3

2 1

0

16M

1Mx16

11x8

R

**

8

**

8*

9

19

18

17

16

15

14

13

12

11

10

C

**

8

**

8*

AP

23*

8*

7

6

5

4

3

2 1

0

64M

8Mx8

12x9

R

9

10

9*

21

20

19

18

17

16

15

14

13

12

11

22

C

9

10

9* 21*

AP

23*

8

7

6

5

4

3

2 1

1

64M

4Mx16

12x8

R

9

8

9*

21

20

19

18

17

16

15

14

13

12

11

10

C

9

8

9* 21*

AP

23*

22*

7

6

5

4

3

2 1

0

64M

2Mx32

11x8

R

9

8

9*

21*

20

19

18

17

16

15

14

13

12

11

10

C

9

8

9* 21*

AP

23*

22*

7

6

5

4

3

2 1

0

128M 16Mx8 12x10

R

9

10

9*

21

20

19

18

17

16

15

14

13

12

11

22

C

9

10

9* 21*

AP

23

8

7

6

5

4 3 2 1

0

128M 8Mx16

12x9

R

9

10

9*

21

20

19

18

17

16

15

14

13

12

11

22

C

9

10

9* 21*

AP

23*

8

7

6

5

4

3

2 1

0

128M 4Mx32

12x8

R

9

8

9*

21

20

19

18

17

16

15

14

13

12

11

10

C

9

8

9* 21*

AP

23*

8*

7

6

5

4

3

2 1

0

256M 32Mx8 13x10

R

9

10

22

21

20

19

18

17

16

15

14

13

12

11

23

C

9

10

22*

21*

AP

24

8

7

6

5

4

3

2 1

0

256M 16Mx16 13x9

R

9

10

22

21

20

19

18

17

16

15

14

13

12

11

23

C

9

10

22*

21*

AP

24*

8

7

6

5

4

3

2 1

0

6.3.2.2

SDRAM Power Up Sequence

The SDRAM must be initialized predefined manner after power on.W90P710 SDRAM Controller

automatically executes the commands needed for initialion and set the mode register of each bank to

default value. The default value is:

— Burst Length = 1

— Burst Type = Sequential (fixed)

— CAS Latency = 2

— Write Burst Length = Burst (fixed)

The value of mode register can be changed after power up sequence by setting the value of

corresponding bank’s configuration register “LENGTH” and “LATENCY” bits and set the MRSET bit

enable to execute the Mode Register Set command.