Rainbow Electronics W90P710CDG User Manual

Page 343

W90P710CD/W90P710CDG

Publication Release Date: September 19, 2006

- 343 -

Revision B2

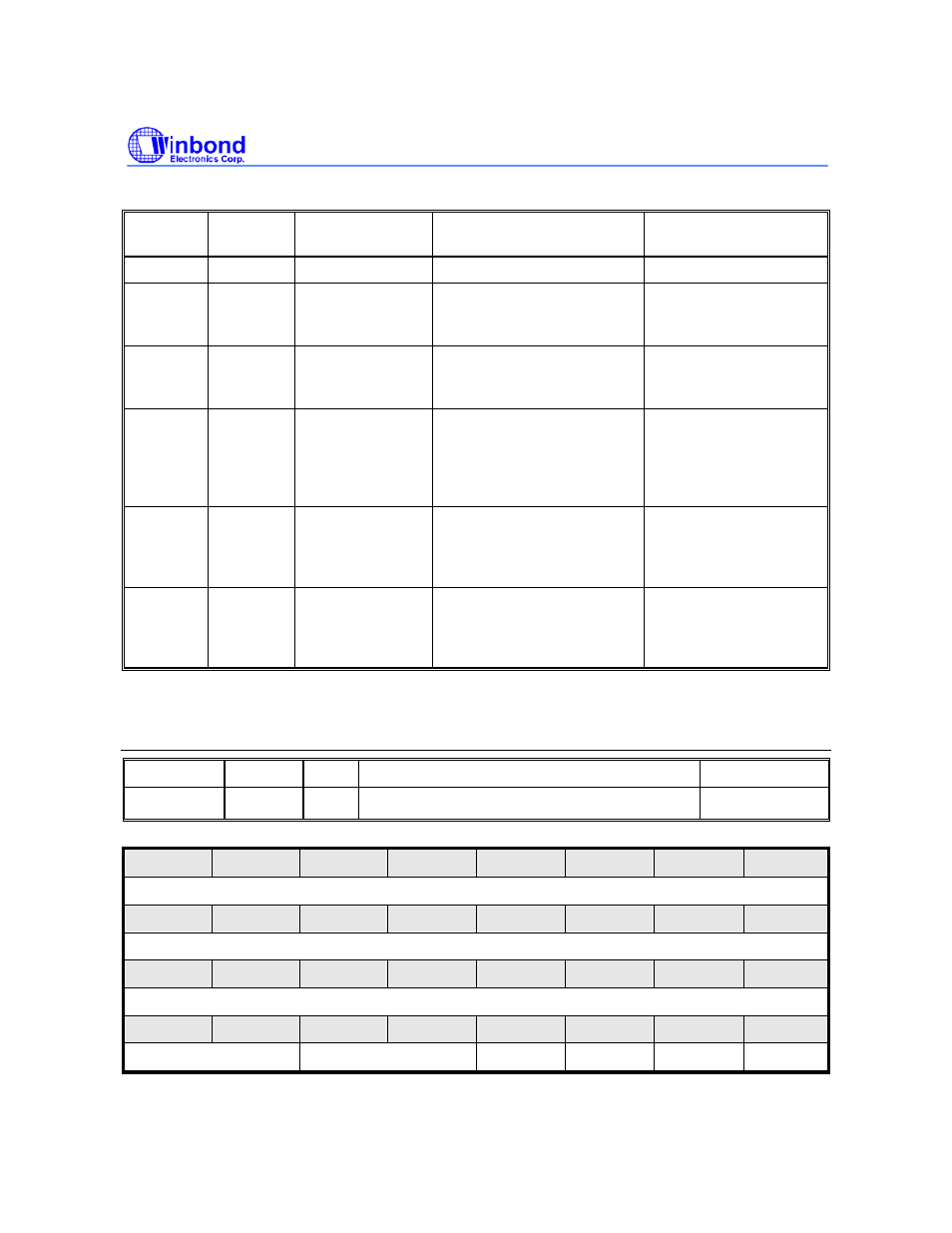

Table 6.12.5.1 Interrupt Control Functions

IIR [3:0]

PRIORITY

INTERRUPT

TYPE

INTERRUPT SOURCE

INTERRUPT RESET

CONTROL

-

-

-

1 --

None

None

--

0110 Highest

Receiver Line

Status (Irpt_RLS)

Overrun error, parity error,

framing error, or break

interrupt

Reading the LSR

0100 Second

Received Data

Available

(Irpt_RDA)

Receiver FIFO threshold

level is reached

Receiver FIFO drops

below the threshold

level

1100 Second

Receiver FIFO

Time-out

(Irpt_TOUT)

Receiver FIFO is non-empty

and no activities are

occurred in the receiver

FIFO during the TOR

defined time duration

Reading the RBR

0010 Third

Transmitter

Holing Register

Empty

(Irpt_THRE)

Transmitter holding register

empty

Reading the IIR (if

source of interrupt is

Irpt_THRE) or writing

into the THR

0000 Fourth

MODEM Status

(Irpt_MOS)

The CTS, DSR, or DCD bits

are changing state or the RI

bit is changing from high to

low.

Reading the MSR

(optional)

Note: These definitions of bit 7, bit 6, bit 5, and bit 4 are different from the 16550

UART FIFO Control Register (UART_FCR)

REGISTER OFFSET R/W

DESCRIPTION

RESET

VALUE

UART_FCR

0x08

W

FIFO Control Register

Undefined

31

30

29

28

27

26

25

24

Reserved

23

22

21

20

19

18

17

16

Reserved

15

14

13

12

11

10

9

8

Reserved

7

6

5

4

3

2

1

0

RFITL

RESERVED

DMS

TFR

RFR

FME