Rainbow Electronics W90P710CDG User Manual

Page 369

W90P710CD/W90P710CDG

Publication Release Date: September 19, 2006

- 369 -

Revision B2

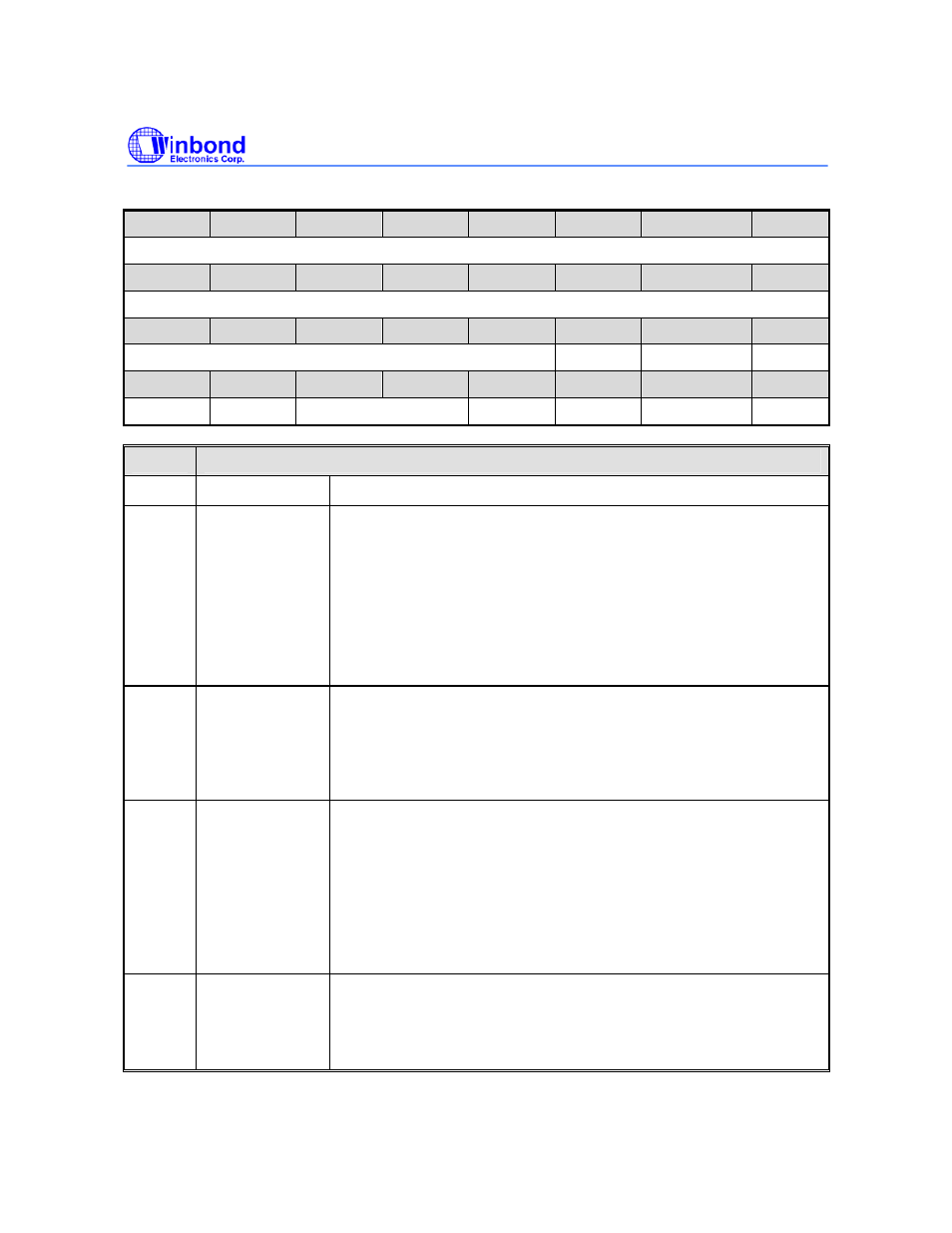

31

30

29

28

27

26

25

24

Reserved

23

22

21

20

19

18

17

16

Reserved

15

14

13

12

11

10

9

8

Reserved WTCLK

nDBGACK_EN WTTME

7

6

5

4

3

2

1

0

WTE WTIE

WTIS

WTIF WTRF WTRE WTR

BITS

DESCRIPTIONS

[31:11]

Reserved Reserved

[10]

WTCLK

Watchdog Timer Clock

This bit is used for deciding whether the Watchdog timer clock input is

divided by 256 or not. Clock source of Watchdog timer is Crystal

input.

0 = Using original clock input

1 = The clock input will be divided by 256

NOTE: When WTTME = 1, set this bit has no effect on WDT clock

(using original clock input).

[9]

nDBGACK_EN

ICE debug mode acknowledge enable

0 = When DBGACK is high, the Watchdog timer counter will be

held

1 = No matter DBGACK is high or not, the Watchdog timer counter

will not be held

[8]

WTTME

Watchdog Timer Test Mode Enable

For reasons of efficiency, the 26-bit counter within the Watchdog

timer is considered as two independent 13-bit counters in the test

mode. They are operated concurrently and separately during the test.

This approach can save a lot of time spent in the test. When the 13-

bit counter overflows, a Watchdog timer interrupt is generated.

0 = Put the Watchdog timer in normal operating mode

1 = Put the Watchdog timer in test mode

[7]

WTE

Watchdog Timer Enable

0 = Disable the Watchdog timer (This action will reset the internal

counter)

1 = Enable the Watchdog timer