Rainbow Electronics W90P710CDG User Manual

Page 441

W90P710CD/W90P710CDG

Publication Release Date: September 19, 2006

- 441 -

Revision B2

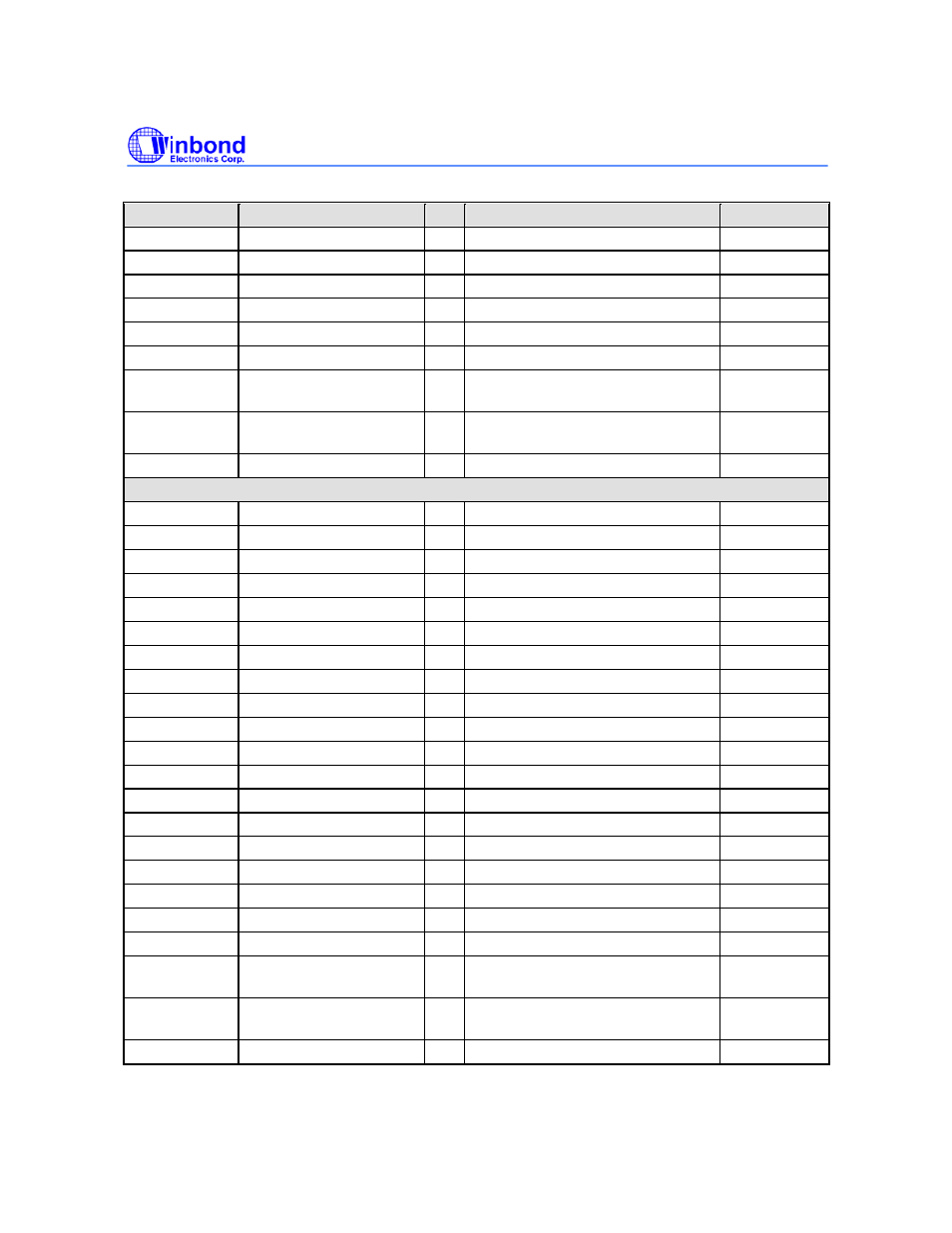

Table 6.12.2.1 Smart Card Host Interface 0 Register Map, continued

REGISTER

ADDRESS

R/W

DESCRIPTION

RESET VALUE

SCHI_TOIR1_0 0xFFF8_5030

R/W Time out Initial Register 1

0x0000_0000

SCHI_TOIR2_0 0xFFF8_5034

R/W Time out Initial Register 2

0x0000_0000

SCHI_TOD0_0 0xFFF8_5038

R Time out Data Register 0

0x0000_00FF

SCHI_TOD1_0 0xFFF8_503C

R Time out Data Register 1

0x0000_00FF

SCHI_TOD2_0 0xFFF8_5040

R Time out Data Register 2

0x0000_00FF

SCHI_BTOR_0 0xFFF8_5044

R/W Buffer Time out Data Register

0x0000_0000

SCHI_BLL_0 0xFFF8_5000

(BDLAB=1) R/W

Baud Rate Divisor Latch Lower Byte

Register

0x0000_001F

SCHI_BLH_0 0xFFF8_5004

(BDLAB=1) R/W

Baud Rate Divisor Latch Higher

Byte Register

0x0000_0000

SCHI_ID_0

0xFFF8_5008 (BDLAB=1) R Smart Card ID Number Register

0x0000_0070

Smartcard Host Interface 1

SCHI_RBR1 0xFFF8_5800

(BDLAB=0) R Receiver Buffer Register

Undefined

SCHI_TBR1 0xFFF8_5800

(BDLAB=0) W Transmitter Buffer Register

Undefined

SCHI_IER1 0xFFF8_5804

(BDLAB=0) R/W Interrupt Enable Register

0x0000_0080

SCHI_ISR1 0xFFF8_5808

(BDLAB=0) R Interrupt Status Register

0X0000_00C1

SCHI_SCFR1 0xFFF8_5808

(BDLAB=0) W Smart

card FIFO Control Register

0x0000_0000

SCHI_SCCR1 0xFFF8_580C

R/W Smart

card Control Register

0x0000_0018

SCHI_CBR1 0xFFF8_5810

R/W Clock Base Register

0x0000_000C

SCHI_SCSR1 0xFFF8_5814

R Smart

Card Status Register

0x0000_0060

SCHI_GTR1 0xFFF8_5818

R/W Guard Rime Register

0x0000_0001

SCHI_ECR1 0xFFF8_581C

R/W Extended Control Register

0x0000_0052

SCHI_TMR1

0xFFF8_5820

R/W Test Mode Register

0x0000_0000

SCHI_TOC1 0xFFF8_5828

R/W Time

out

Configuration Register

0x0000_0000

SCHI_TOIR0_1 0xFFF8_582C

R/W Time out Initial Register 0

0x0000_0000

SCHI_TOIR1_1 0xFFF8_5830

R/W Time out Initial Register 1

0x0000_0000

SCHI_TOIR2_1 0xFFF8_5834

R/W Time out Initial Register 2

0x0000_0000

SCHI_TOD0_1 0xFFF8_5838

R Time out Data Register 0

0x0000_00FF

SCHI_TOD1_1 0xFFF8_583C

R Time out Data Register 1

0x0000_00FF

SCHI_TOD2_1 0xFFF8_5840

R Time out Data Register 2

0x0000_00FF

SCHI_BTOR1 0xFFF8_5844

R/W Buffer

Time out Data Register

0x0000_0000

SCHI_BLL1 0xFFF8_5800

(BDLAB=1) R/W

Baud Rate Divisor Latch Lower Byte

Register

0x0000_001F

SCHI_BLH1 0xFFF8_5804

(BDLAB=1) R/W

Baud Rate Divisor Latch Higher

Byte Register

0x0000_0000

SCHI_ID1

0xFFF8_5808 (BDLAB=1) R Smart Card ID Number Register

0x0000_0070